CS创世SD NAND的存储芯片应用方案

前言:

很感谢深圳雷龙发展有限公司为博主提供的两片SD NAND的存储芯片,在这里博主记录一下自己的使用过程以及部分设计。

深入了解该产品:

拿到这个产品之后,我大致了解了下两款芯片的性能。CSNP4GCR01-AMW是一种基于NAND闪存和SD控制器的4Gb密度嵌入式存储;而CSNP32GCR01-AOW是一种基于NAND闪存和SD控制器的32Gb密度嵌入式存储。与原始NAND相比其具有嵌入式坏块管理和更强的嵌入式ECC。即使在异常断电,它仍然可以安全地保存数据。作为一个存储芯片,它确实做到了小巧,LGA-8的封装对比我之前用到过的TF卡,只占到了其面积的三分之一,这样对于一些嵌入式的设计就方便了很多。

雷龙官方还很贴心的提供了样品的测试板,在这款测试板上,我焊接了4GB的CSNP4GCR01-AMW上去,并且跑了一下分,对于一款小的存储芯片而言,实在难得。

(上图为测试板焊接图)

博主日前在设计基于H616与NB-IOT的嵌入式智能储物柜的时候考虑过存储方面的问题,当时在SD NAND和EMMC与TF卡中徘徊,以下是几个存储类型的对比。

经过多方对比,本着不需要频繁更换的原则,同时也为了更好的防水和成本考虑,最终决定使用雷龙公司的SD NAND 作为设计样品的存储部分。

此外,SD NAND还具有不用写驱动程序自带坏块管理的NAND FLASH(贴片式TF卡),不标准的SDIO接口,也同时兼容SPI/SD接口,10万次的SLC晶圆擦写寿命,通过一万次的随机掉电测试耐高低温,经过跑分测得,速度级别Class10。标准的SD2.0协议,普通的SD卡可以直接驱动,支持TF卡启动的SOC都可以用SD NAND,而且雷龙官方还贴心的提供了STM32参考例程和原厂技术支持,这对于刚上手的小白而言,十分友好。

设计理念:

使用H616作为主控CPU并搭配NB-IOT来向申请下来的云端传输数据,当WIFI正常时,储物数据每搁两小时向云端传输一次,当有人取出物品时再次向云端发送一次数据(不保留在SD NAND中);一旦系统检测到WIFI出现问题,储物数据转而存储到SD NAND中,取物时输入的物品ID和取出时间一并放入SD NAND中(我也是看中了SD NAND与原始NAND相比其具有嵌入式坏块管理和更强的嵌入式ECC。即使在异常断电,它仍然可以安全地保存数据这一点)。

部分SD NAND的参考设计

根据官方数据手册提供的SD NAND参考设计,只占用8个GPIO,对于H616来说,确实很友好

这里为了不泄露他人的劳动成果,我也就不粘PCB设计了。

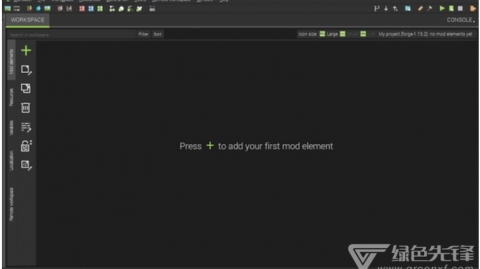

采用H616驱动SD NAND的示例代码

下面是关于H616驱动SD NAND的示例代码,这里记录一下自己当初的学习过程(注:这个代码不能直接拿过来就用,而是要根据自己的需求修改)

#include <stdio.h>#include <stdint.h>#include <stdlib.h>#include <string.h>#include "h616_sdio.h"// 定义SDIO引脚#define SDIO_CMD_PIN 0#define SDIO_CLK_PIN 1#define SDIO_D0_PIN 2#define SDIO_D1_PIN 3#define SDIO_D2_PIN 4#define SDIO_D3_PIN 5// 定义NAND芯片命令#define CMD_READ 0x00#define CMD_WRITE 0x80#define CMD_ERASE 0x60#define CMD_STATUS 0x70#define CMD_RESET 0xff// 定义NAND芯片状态#define STATUS_READY 0x40#define STATUS_ERROR 0x01// 初始化SDIO控制器void sdio_init(){// 设置SDIO引脚模式和速率h616_sdio_set_pin_mode(SDIO_CMD_PIN, H616_SDIO_PIN_MODE_SDIO);h616_sdio_set_pin_mode(SDIO_CLK_PIN, H616_SDIO_PIN_MODE_SDIO);h616_sdio_set_pin_mode(SDIO_D0_PIN, H616_SDIO_PIN_MODE_SDIO);h616_sdio_set_pin_mode(SDIO_D1_PIN, H616_SDIO_PIN_MODE_SDIO);h616_sdio_set_pin_mode(SDIO_D2_PIN, H616_SDIO_PIN_MODE_SDIO);h616_sdio_set_pin_mode(SDIO_D3_PIN, H616_SDIO_PIN_MODE_SDIO);h616_sdio_set_clock(H616_SDIO_CLOCK_FREQ_25MHZ);// 初始化SDIO控制器h616_sdio_init();}// 发送NAND芯片命令void nand_send_cmd(uint8_t cmd){// 设置SDIO控制器传输模式和命令码h616_sdio_set_transfer_mode(H616_SDIO_TRANSFER_MODE_WRITE);h616_sdio_set_command_code(cmd);// 发送命令h616_sdio_send_command();}// 发送NAND芯片地址void nand_send_addr(uint32_t addr){// 设置SDIO控制器传输模式和地址h616_sdio_set_transfer_mode(H616_SDIO_TRANSFER_MODE_WRITE);h616_sdio_set_address(addr);// 发送地址h616_sdio_send_address();}// 读取NAND芯片数据void nand_read_data(uint8_t *data, uint32_t size){// 设置SDIO控制器传输模式h616_sdio_set_transfer_mode(H616_SDIO_TRANSFER_MODE_READ);// 读取数据h616_sdio_read_data(data, size);}// 写入NAND芯片数据void nand_write_data(const uint8_t *data, uint32_t size){// 设置SDIO控制器传输模式h616_sdio_set_transfer_mode(H616_SDIO_TRANSFER_MODE_WRITE);// 写入数据h616_sdio_write_data(data, size);}// 读取NAND芯片状态uint8_t nand_read_status(){uint8_t status;// 发送读取状态命令nand_send_cmd(CMD_STATUS);// 读取状态nand_read_data(&status, 1);return status;}// 等待NAND芯片准备就绪void nand_wait_ready(){uint8_t status;// 循环读取状态,直到NAND芯片准备就绪do {status = nand_read_status();} while ((status & STATUS_READY) == 0);}// 读取NAND芯片数据void nand_read(uint32_t page, uint32_t column, uint8_t *data, uint32_t size){// 发送读取命令和地址nand_send_cmd(CMD_READ);nand_send_addr(column | (page << 8));// 等待NAND芯片准备就绪nand_wait_ready();// 读取数据nand_read_data(data, size);}// 写入NAND芯片数据void nand_write(uint32_t page, uint32_t column, const uint8_t *data, uint32_t size){// 发送写入命令和地址nand_send_cmd(CMD_WRITE);nand_send_addr(column | (page << 8));// 写入数据nand_write_data(data, size);// 等待NAND芯片准备就绪nand_wait_ready();}// 擦除NAND芯片块void nand_erase(uint32_t block){// 发送擦除命令和地址nand_send_cmd(CMD_ERASE);nand_send_addr(block << 8);// 等待NAND芯片准备就绪nand_wait_ready();}// 复位NAND芯片void nand_reset(){// 发送复位命令nand_send_cmd(CMD_RESET);// 等待NAND芯片准备就绪nand_wait_ready();}// 示例程序入口int main(){uint8_t data[2048];memset(data, 0x5a, sizeof(data));// 初始化SDIO控制器sdio_init();// 复位NAND芯片nand_reset();// 擦除第0块nand_erase(0);// 写入第0页nand_write(0, 0, data, sizeof(data));// 读取第0页nand_read(0, 0, data, sizeof(data));return 0;}————————————————

【本文转载自CSDN,作者:孙启尧】

智能座舱之存储篇第三篇---NAND Flash 一眼就看明白了

上期内容我们重点说了NAND FLASH本身的一些特殊性,比如写之前要进行擦除,而且存在坏块的可能性性,所以很多车厂在评估NAND FLASH的时候,会评估目前容量的冗余量是多少,要保障有足够多的空间去预防坏块的产生后的数据搬移。

这期内容重点说说NAND FLASH的一些操作特性,怎么进行控制和读取的。这期的内容有点硬核,需要有一些专业知识的人进行阅读,科普类的文章咱们下期继续。

NAND FLASH的硬件特性介绍

上图是镁光 NAND FLASH MT29F1G08ABAEAH4的引脚(Pin)所对应的功能,简单翻译如下:

1. I/O0 ~ I/O7:用于输入地址/数据/命令,输出数据

2. CLE:Command Latch Enable,命令锁存使能,在输入命令之前,要先在模式寄存器中,设置CLE使能

3. ALE:Address Latch Enable,地址锁存使能,在输入地址之前,要先在模式寄存器中,设置ALE使能

4. CE#:Chip Enable,芯片使能,在操作Nand Flash之前,要先选中此芯片,才能操作

5. RE#:Read Enable,读使能,在读取数据之前,要先使CE#有效。

6. WE#:Write Enable,写使能,在写取数据之前,要先使WE#有效。

7. WP#:Write Protect,写保护

8. R/B#:Ready/Busy Output,就绪/忙,主要用于在发送完编程/擦除命令后,检测这些操作是否完成,忙,表示编程/擦除操作仍在进行中,就绪表示操作完成.

9. Vcc:Power,电源

10. Vss:Ground,接地

11. N.C:Non-Connection,未定义,未连接。

实际项目的NAND FLASH原理图

上图中我们可以发现有两个地方需要上拉电阻R/B#:、WP#,其他都是CPU同nand flash直接相连接。通过查询flash 的datasheet可以发现,这两个引脚是开漏极输出,需要上拉电阻。

而且可以看到电路设计中WP#引脚一端接上拉电阻,一端通过二极管和0欧姆电阻连接到CPU复位引脚,CPU主芯片平台的复位是低电平复位,WP#引脚是低电平的时候写保护有效,这样做的目的就是,在复位期间,即CPU复位引脚为低电平期间此时WP#引脚也为二极管电压(0.7V)为低电平,为写保护状态,在复位期间,CPU引脚状态不定,容易对flash进行误操作。这样做的目的就是硬件实现在CPU复位期间,flash是写保护状态,不允许写入的。

很多时候掉电产生的擦除数据,导致数据丢失无法开机、无法保存掉电记忆等等问题都可以使用这个方案来对策解决问题。

为何需要ALE和CLE

比如命令锁存使能(Command Latch Enable,CLE)和地址锁存使能(Address Latch Enable,ALE),那是因为,Nand Flash就8个I/O,而且是复用的,也就是,可以传数据,也可以传地址,也可以传命令,为了区分你当前传入的到底是啥,所以,先要用发一个CLE(或ALE)命令,告诉nand Flash的控制器一声,我下面要传的是命令(或地址),这样,里面才能根据传入的内容,进行对应的动作。否则,nand flash内部,怎么知道你传入的是数据,还是地址,还是命令啊,也就无法实现正确的操作了。

Nand Flash只有8个I/O引脚的好处

1. 减少外围引脚:相对于并口(Parellel)的Nor Flash的48或52个引脚来说,的确是大大减小了引脚数目,这样封装后的芯片体积,就小很多。现在芯片在向体积更小,功能更强,功耗更低发展,减小芯片体积,就是很大的优势。同时,减少芯片接口,也意味着使用此芯片的相关的外围电路会更简化,避免了繁琐的硬件连线。

2. 提高系统的可扩展性,因为没有像其他设备一样用物理大小对应的完全数目的addr引脚,在芯片内部换了芯片的大小等的改动,对于用全部的地址addr的引脚,那么就会引起这些引脚数目的增加,比如容量扩大一倍,地址空间/寻址空间扩大一倍,所以,地址线数目/addr引脚数目,就要多加一个,而对于统一用8个I/O的引脚的Nand Flash,由于对外提供的都是统一的8个引脚,内部的芯片大小的变化或者其他的变化,对于外部使用者(比如编写nand flash驱动的人)来说,不需要关心,只是保证新的芯片,还是遵循同样的接口,同样的时序,同样的命令,就可以了。这样就提高了系统的扩展性。

片选无关(CE don’t-care)技术

Nand flash支持一个叫做CE don’t-care的技术,字面意思就是,不关心是否片选,那有人会问了,

如果不片选,那还能对其操作吗?答案就是,这个技术,主要用在当时是不需要选中芯片却还可以继续操作的这些情况:在某些应用,比如录音,音频播放等应用中,外部使用的微秒(us)级的时钟周期,此处假设是比较少的2us,在进行读取一页或者对页编程时,是对Nand Flash操作,这样的串行(Serial Access)访问的周期都是20/30/50ns,都是纳秒(ns)级的,此处假设是50ns,当你已经发了对应的读或写的命令之后,接下来只是需要Nand Flash内部去自己操作,将数据读取除了或写入进去到内部的数据寄存器中而已,此处,如果可以把片选取消,CE#是低电平有效,取消片选就是拉高电平,这样会在下一个外部命令发送过来之前,即微秒量级的时间里面,即2us-50ns≈2us,这段时间的取消片选,可以降低很少的系统功耗,但是多次的操作,就可以在很大程度上降低整体的功耗了。

总结起来简单解释就是:由于某些外部应用的频率比较低,而Nand Flash内部操作速度比较快,所以具体读写操作的大部分时间里面,都是在等待外部命令的输入,同时却选中芯片,产生了多余的功耗,此“不关心片选”技术,就是在Nand Flash的内部的相对快速的操作(读或写)完成之后,就取消片选,以节省系统功耗。待下次外部命令/数据/地址输入来的时候,再选中芯片,即可正常继续操作了。这样,整体上,就可以大大降低系统功耗了。

NAND FLASH 的读操作详细解读

以最简单的read操作为例,解释如何理解时序图,以及将时序图中的要求,转化为代码。解释时序图之前,让我们先要搞清楚,我们要做的事情:那就是,要从nand flash的某个页里面,读取我们要的数据。要实现此功能,会涉及到几部分的知识,至少很容易想到的就是:需要用到哪些命令,怎么发这些命令,怎么计算所需要的地址,怎么读取我们要的数据等等。

就好比你去图书馆借书,想想是一个什么样的流程,首先得告诉馆长你要要借书还是还书、然后把要借书的位置告诉馆长,最后是把图书卡或者借书证件给馆长,此时就耐心等待要借的书籍了。

下面,就一步步的解释,需要做什么,以及如何去做:

1.需要使用何种命令

首先,是要了解,对于读取数据,要用什么命令。

下面是datasheet中的命令集合:

很容易看出,我们要读取数据,要用到Read命令,该命令需要2个周期,第一个周期发0x00,第二个周期发0x30。

2.发送命令前的准备工作以及时序图各个信号的具体含义

知道了用何命令后,再去了解如何发送这些命令。

Nand Flash数据读取操作的时序图

注:此图来自镁光的型号MT29F1G08ABAEAH4:E的nand flash的数据手册(datasheet)。

我们来一起看看,我在图中的特意标注的①边上的红色竖线。

红色竖线所处的时刻,是在发送读操作的第一个周期的命令0x00之前的那一刻。让我们看看,在那一刻,其所穿过好几行都对应什么值,以及进一步理解,为何要那个值。

(1)红色竖线穿过的第一行,是CLE。还记得前面介绍命令所存使能(CLE)那个引脚吧?CLE,将CLE置1,就说明你将要通过I/O复用端口发送进入Nand Flash的,是命令,而不是地址或者其他类型的数据。只有这样将CLE置1,使其有效,才能去通知了内部硬件逻辑,你接下来将收到的是命令,内部硬件逻辑,才会将受到的命令,放到命令寄存器中,才能实现后面正确的操作,否则,不去将CLE置1使其有效,硬件会无所适从,不知道你传入的到底是数据还是命令了。

(2)而第二行,是CE#,那一刻的值是0。这个道理很简单,你既然要向Nand Flash发命令,那么先要选中它,所以,要保证CE#为低电平,使其有效,也就是片选有效。

(3)第三行是WE#,意思是写使能。因为接下来是往nand Flash里面写命令,所以,要使得WE#有效,所以设为低电平。

(4)第四行,是ALE是低电平,而ALE是高电平有效,此时意思就是使其无效。而对应地,前面介绍的,使CLE有效,因为将要数据的是命令,而不是地址。如果在其他某些场合,比如接下来的要输入地址的时候,就要使其有效,而使CLE无效了。

(5)第五行,RE#,此时是高电平,无效。可以看到,知道后面低6阶段,才变成低电平,才有效,因为那时候,要发生读取命令,去读取数据。

(6)第六行,就是我们重点要介绍的,复用的输入输出I/O端口了,此刻,还没有输入数据,接下来,在不同的阶段,会输入或输出不同的数据/地址。

(7)第七行,R/B#,高电平,表示R(Ready)/就绪,因为到了后面的第5阶段,硬件内部,在第四阶段,接受了外界的读取命令后,把该页的数据一点点送到页寄存器中,这段时间,属于系统在忙着干活,属于忙的阶段,所以,R/B#才变成低,表示Busy忙的状态的。

介绍了时刻①的各个信号的值,以及为何是这个值之后,相信,后面的各个时刻,对应的不同信号的各个值,大家就会自己慢慢分析了,也就容易理解具体的操作顺序和原理了。

3.如何计算出,我们要传入的地址

在介绍具体读取数据的详细流程之前,还要做一件事,那就是,先要搞懂我们要访问的地址,以及这些地址,如何分解后,一点点传入进去,使得硬件能识别才行。

此处还是以MT29F1G08ABAEAH4:E为例,此nand flash,一共有1024个块,每个块内有64页,每个页是2K+64 Bytes,假设,我们要访问其中的第1000个块中的第25页中的1208字节处的地址,此时,我们就要先把具体的地址算出来:

物理地址=块大小×块号+页大小×页号+页内地址=1000×128K+2K×25+1208=0x7D0CCB8,接下来,我们就看看,怎么才能把这个实际的物理地址,转化为nand Flash所要求的格式。

在解释地址组成之前,先要来看看其datasheet中关于地址周期的介绍:

图 Nand Flash的地址周期组成

结合时序图的2,3阶段,我们可以看出,此nand flash地址周期共有4个,2个列(Column)周期,2个行(Row)周期。

而对于对应的,我们可以看出,实际上,列地址CA0~CA10,就是页内地址,11位地址范围是从0到2047,即2K,而多出的A11,理论上可以表示2048~4095,但是实际上,上述规格书中说明当CA11为1时,CA【10:6】都必须为0,所以我们最多也只用到了2048~2112,用于表示页内的oob区域,其大小是64字节。

PA0~PA5,称作页号,页的号码,可以定位到具体是哪一个页。由6个位控制,最多寻址64页,符合规格书中的一块有64页。

而其中,BA6~BA15,表示对应的块号,即属于哪个块,有10个位控制,寻址范围为1024个块。

// 可见:地址的传输顺序是是 页内地址,页号,块号。从小到大。

简单解释完了地址组成,那么就很容易分析上面例子中的地址了:

0x7D0CCB8 = 0111 1101 0000 1100 0000 1100 1011 1000,分别分配到4个地址周期就是:

1st 周期,CA7~CA0 :1011 1000 = 0x B8

2nd周期,CA11~CA8 :0000 1100 = 0x 0C

3rd周期,BA7~PA0 :0000 1100 = 0x 0C

4th周期,A27~A20 :0111 1101 = 0x 7D

注意,上图图中对应的,*L,意思是低电平,由于未用到那些位,datasheet中强制要求设为0,所以,才有上面的2nd周期中的高4位是0000.。因此,接下来要介绍的,我们要访问第1000个块中的第25页中的1208字节处的话,所要传入的地址就是分4个周期,分别传入2个列地址的:0xB8,0x0C,然后再传2个行地址的:0x0C,0x7D,这样硬件才能识别。

4.读操作过程的解释

准备工作终于完了,下面就可以开始解释说明,对于读操作的,上面图中标出来的,1-6个阶段,具体是什么含义。

(1) 操作准备阶段:此处是读(Read)操作,所以,先发一个图5中读命令的第一个阶段的0x00,表示,让硬件先准备一下,接下来的操作是读。

(2) 发送两个周期的列地址。也就是页内地址,表示,我要从一个页的什么位置开始读取数据。

(3) 接下来再传入三个行地址。对应的也就是页号。

(4) 然后再发一个读操作的第二个周期的命令0x30。接下来,就是硬件内部自己的事情了。

(5)Nand Flash内部硬件逻辑,负责去按照你的要求,根据传入的地址,找到哪个块中的哪个页,然后把整个这一页的数据,都一点点搬运到页缓存中去。而在此期间,你所能做的事,也就只需要去读取状态寄存器,看看对应的位的值,也就是R/B#那一位,是1还是0,0的话,就表示,系统是busy,仍在”忙“(着读取数据),如果是1,就说系统活干完了,忙清了,已经把整个页的数据都搬运到页缓存里去了,你可以接下来读取你要的数据了。

对于这里。估计有人会问了,这一个页一共2048+64字节,如果我传入的页内地址,就像上面给的1028一类的值,只是想读取1028到2011这部分数据,而不是页开始的0地址整个页的数据,那么内部硬件却读取整个页的数据出来,岂不是很浪费吗?答案是,的确很浪费,效率看起来不高,但是实际就是这么做的,而且本身读取整个页的数据,相对时间并不长,而且读出来之后,内部数据指针会定位到你刚才所制定的1208的那个位置。

(6) 接下来,就是“窃取“系统忙了半天之后的劳动成果的时候了,呵呵。通过先去Nand Flash的控制器中的数据寄存器中写入你要读取多少个字节(byte)/字(word),然后就可以去Nand Flash的控制器的FIFO中,一点点读取你要的数据了。

至此,整个Nand Flash的读操作就完成了。

对于其他操作,可以根据上面的分析,一点点自己去看datasheet,根据里面的时序图去分析具体的操作过程,然后对照代码,会更加清楚具体是如何实现的。

NAND FLASH 搭配NOR FLASH的优缺点

常见的应用组合就是,用小容量的Nor Flash存储启动代码,比如uboot,系统启动后,初始化对应的硬件,包括SDRAM等,然后将Nand Flash上的Linux 内核读取到内存中,做好该做的事情后,就跳转到SDRAM中去执行内核了。

这样的好处是由于NAND 本身有坏块的可能性,所以为了保障启动万无一失,很多要求高级安全的产品,标注必须从NOR Flash启动uboot,而且从NOR启动还有一个好处就是启动速度快,NAND Flash的优点是容量大,但是读取速度不快,比不上NOR Flash,比如一些对于开机速度有要求的产品应用,比如车载液晶仪表,这类产品为了快速启动一般都是NOR FLASH+EMMC的配置,当然像赛普拉斯平台直接上hyperflash那就更快了。

NAND Flash的ECC校验简单说明

我们先来说说为什么需要ECC校验这个事情,其实上一篇文章我们说过由于NAND flash的自身的不稳定性,存在位翻转的现象,所以就存在写入到flash中的数据和读出来的数据不一样的情况发生,此时就需要有一个检验的机制,防止读出来的不正确,还可以纠正过来。

其实这个就类似于去银行存钱,你存了1W,过几天去银行去取钱的时候发现只有9000了,这个时候你就会拿出存条找银行理论,上次明明存的就是1W啊,你少的1000必须跟我纠正过来,其实这个就是NAND flash的ECC检验原理,发现有读出来的数据和存进去的数据不正确,此时就需要去纠正回来,当然这里的纠正的数据是有限制的,不是所有数据出错都能纠正过来。

ECC 校验是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成 ECC 校验码。它能够检测并纠正单比特错误和检测双比特错误,但对双比特以上的错误不能保证检测。它克服了传统奇偶校验只能检出奇数位出错、校验码冗长、不能纠错的局限性。每 nbit 的 Ecc 数值可满足 2的n次方bit 数据包的校验要求。

当往Nand Flash 的Page 中写入数据的时候,每256字节我们生成一个ECC 校验和,称之为原ECC校验和,保存到 PAGE 的OOB数据区中。当从Nand Flash 中读取数据的时候,每 256 字节我们生成一个ECC校验和,称之为新 ECC 校验和。

校验的时候,根据上述ECC生成原理不难推断:将从 OOB 区中读出的原 ECC校验和新ECC校验和按位异或,若结果为0,则表示不存在错(或是出现了ECC无法检测的错误):若3个字节异或结果中存在11个比特位为1,表示存在一个比特错误,且可纠正;若3个字节异或结果中只存在1个比特位为1,表示OOB区出错:其他情况均表示出现了无法纠正的错误。

这两期我们基本上把NAND FLASH的相关设计和使用都完整讲了一遍,下期会讲讲车载DRAM和EMMC的相关内容,敬请期待。

相关问答

如何让U-boot实现 Nand /Nor双启动?这时候,Uboot通过另外的代码,实际是Nandsubsystem部分,把kernel从Nand读到内存上,再通过指令,然后CPU跳到Kernel入口地址执行。一旦Kernel跑起来,Kerne...

飞凌开发板6410uboot什么 命令 擦除nandflash啊?sferase+起始地址+擦查长度在uboot下输入help可以查看所有的命令sferase+起始地址+擦查长度在uboot下输入help可以查看所有的命令

s3c2410是单片机吗?S3C2410处理器是Samsung公司基于ARM公司的ARM920T处理器核,采用FBGA封装,采用0.18um制造工艺的32位微控制器。该处理器拥有:独立的16KB指令Cache和16KB数据Ca...

U盘怎样存储数据?U盘存储数据的原理为:计算机把二进制数字信号转为复合二进制数字信号(加入分配、核对、堆栈等指令)读写到USB芯片适配接口,通过芯片处理信号分配给NANDFLASH...

M.2接口的固态硬盘,有何优势?目前市面上比较广泛的M2接口的硬盘分为两种,一种是SATA总线的硬盘,一种是NVME协议的硬盘。先来说说SATA总线的M2硬盘这种硬盘跟NVME协议的M2硬盘,大小.外观...

单片机能存储多大的数据?8位CPU进行运算控制布尔代数处理器,具有运算能力128内部RAM数据存储4kb内部掩模ROM程序储存器两个16位可编程定时/计数器32个(4x8位)双向可独立寻址的I/O...

麒麟980将会比麒麟970有何重大提升?“麒麟980将全面超越高通骁龙845和苹果A11。”8月初时华为华为消费者业务CEO余承东在宣布上半年业务时,提及华为新一代芯片麒麟980时说了这么一句话。同时他...

2019年有哪些值得期待的PC DIY产品?自己的电脑用了快五年了,硬件配置早就有些落伍了(暗黑、魔兽倒是无压力),不止一次想过升级,但是作为一名等等党,每次升级的时候都希望有完美的技术出现了再...如...

半岛平台下载(官方)APP下载安装/网站网页通用版入口英特尔520系列120GB固态硬盘特尔固态硬盘520可提供高达80,000次的4K随机写入IOPS(每秒输入输出操作)性能以及高达50,000次的4K随机读取IOPS性能,...

手机闪存怎么查?怎么测试?鲁大师安卓发布新版v8.2.6,为ROM测试项目“体验评测”新增测试栏“闪存测试”,用更为通用的内存写入速度,例如100MB/s,让消费者更容易横向对比,让手机体验评...