微米让智能手机和平板电脑续航能力增强

微米在昨天宣布它优化了移动设备3d NAND内存技术。对于消费者来说,这意味着一个智能手机或平板电脑将拥有一块更大的电池,3d NAND数据存储细胞垂直而不是传播出来像“平面”的存储设备,目前该项技术仅应用于智能手机、平板电脑和闪存。

据微米报道,其新的3d NAND内存模小于30%的典型平面。指标测试只有60.217平房毫米,是行业迄今为止最小的3d NAND芯片。这种技术也可用于低功耗LPDDR4X内存模块,比LPDDR4X记忆模块多提供20%的能源效率。

微米这项新技术,解决了设备的移动内存和存储需求等问题。为用户带来前所未有的全新体验,包括无缝高清视频流,更高的宽带游戏,更快地启动时间,相机的性能,和文件加载能力。官方还表示,预计要在2016年底将新的3d NAND 技术普及到大部分用户。

3D NAND,1000层

据Xtech Nikkei报道,Kioxia 首席技术官 (CTO) Hidefumi Miyajima 表示,该公司计划到 2031 年批量生产超过 1,000 层的 3D NAND 内存。在东京城市大学举行的第 71 届应用物理学会春季会议上的演讲中,Miyajima 讨论了在 3D NAND 器件中实现超过 1000 层的技术挑战和解决方案。

增加 3D NAND 器件中的有源层数量是当今提高闪存记录密度的最佳方法,因此所有 3D NAND 制造商都努力每 1.5 到 2 年就推出新的工艺节点来实现这一目标。每个新节点都会带来一些挑战,因为 3D NAND 制造商必须增加层数并横向和纵向缩小 NAND 单元。这个过程要求制造商在每个新节点都采用新材料,这是一项重大的研发挑战。

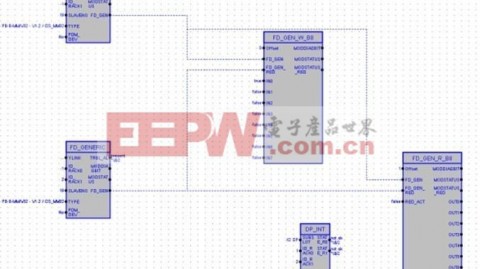

图1:NAND 闪存公司正在竞相开发通过高堆叠增加容量的技术。

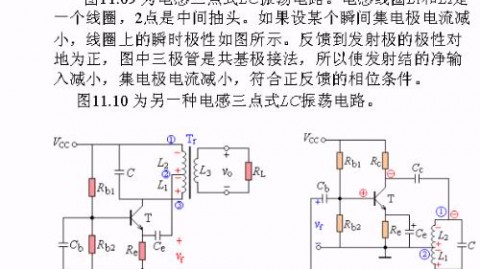

2013年前后,NAND Flash的容量提升方式从小型化转向分层化。目前,各家公司都在竞相量产200层以上的3D NAND(图1)。小型化的限制是由于器件操作的物理限制和光刻成本的增加,但对于堆叠而言,“如何降低工艺成本已成为与光刻一样大的问题。”

蚀刻工艺对制造成本的影响特别大。3D NAND 的多层薄膜形成后,通过等离子蚀刻产生大量孔(存储孔),从顶层贯穿底层。该工艺是通过在孔中沉积氧化膜、氮化膜等来制造多层存储单元。

内存孔的直径约为100纳米,深度为数微米,因此能够快速、均匀地钻出大深宽比孔的蚀刻技术至关重要。每 300mm 晶圆上的存储孔数量达到数万亿个。

这种蚀刻工艺“大约需要一个小时。因为需要时间,所以需要增加设备数量,使其成为(对于3D NAND)成本最高的工艺”。随着堆叠层数的增加以及存储孔的深宽比的增加,蚀刻所需的时间呈指数增长,从而增加了制造成本。均匀加工难度的增加也往往是降低产量的一个因素。

因此,对于Kioxia的第8代产品,我们没有一次性构建218层,而是采用了分两步构建的方法。但又增加了新的困难,比如需要将下层和上层的内存孔完美对齐。

如今,Kioxia 最好的 3D NAND 器件是第八代 BiCS 3D NAND 存储器,具有 218 个有源层和 3.2 GT/s 接口(于 2023 年 3 月首次推出)。这一代引入了一种新颖的CBA(CMOS直接键合到阵列)架构,该架构涉及使用最合适的工艺技术单独制造3D NAND单元阵列晶圆和I/O CMOS晶圆并将它们键合在一起。其结果是产品具有增强的位密度和改进的 NAND I/O 速度,这确保了内存可用于构建最好的 SSD。

与此同时,Kioxia 及其制造合作伙伴 Western Digital 尚未披露 CBA 架构的具体细节,例如 I/O CMOS 晶圆是否包括额外的 NAND 外围电路(如页缓冲器(page buffers)、读出放大器和电荷泵)。通过分别生产存储单元和外围电路,制造商可以为每个组件利用最高效的工艺技术,随着行业向串堆叠等方法发展,制造商将获得更多优势,串堆叠肯定会用于 1,000 层 3D NAND。

值得注意的是,三星还预计将实现量产级1000层3D NAND。根据2022年9月的报道,该公司目前正在设计第 9 代和第 10 代 V-NAND 并进行原型设计,与当今的技术相比,层密度适当增加。三星目前正在出货其第七代 176 层 V-NAND,并计划在今年年底前发布基于其第八代 230 层设计的 V-NAND 芯片。后者采用 512 Gb 芯片,密度将提高 42%。

但三星正着眼于密度的更大幅度跃升,并预计到 2030 年实现 1,000 层 V-NAND 设计。三星还继续致力于 QLC(四级单元)技术,希望在提高存储位的同时提高性能密度。

3D-NAND 的层数有限制吗?

回顾 2D NAND,它采用平面架构,浮动栅极 (FG) 和外围电路彼此相邻。2007年,随着2D NAND的尺寸达到极限,东芝提出了3D NAND结构。

三星于 2013 年率先向市场推出了所谓的“V-NAND”。

3D 设计引入了多晶硅和二氧化硅的交替层,并将浮动栅极替换为电荷陷阱闪存 (CTF)。这些区别既有技术上的,也有经济上的。FG 将存储器存储在导电层中,而 CTF 将电荷“捕获”在介电层内。由于制造成本降低,CTF 设计很快成为首选,但当然不是唯一的。

IBM 研究员 Roman Pletka 指出:“尽管所有制造商都转向电荷陷阱单元架构,但我预计传统浮栅单元在未来仍将发挥不可忽视的作用,特别是对于容量或保留敏感的用例。”

然而,Hynix 表示,尽管采用了摩天大楼式堆叠的创新,但第一代 3D NAND 设计仍将外围电路保留在一侧。

最终,3D NAND 供应商将外围电路移至 CTF 下。用 SK Hynix 的术语来说,它现在是 Periphery Under Cell (PUC) 层。一方面,“4D NAND”比 CTF/PUC NAND 更短、更酷。另一方面,这最终是 3D NAND 的另一种变体,单位单元面积更小。针对较小占地面积的类似设计有不同的商标名称,例如 Micron 的 CMOS under Array (CuA)。

美光科技在 2022 年 7 月下旬宣布推出 232 层 NAND,并已投入生产,因此获得了吹嘘的资本。根据该公司的新闻稿,美光表示,其 232 层 NAND 是存储创新的分水岭,也是将 3D NAND 生产扩展到 200 层以上的能力的第一个证明。

美光还声称 业界最快的 NAND I/O 速度为 2.4 Gbps,与上一代产品相比,每个芯片的写入带宽提高了 100%,读取带宽提高了 75% 以上。此外,232层NAND包含六平面TLC生产NAND,美光表示这是所有TLC闪存中每个芯片最多的平面,并且每个平面都具有独立的读取能力。

业内分析人士认为,这可能是此次公告中最令人印象深刻的部分。由于有六个平面,该芯片的表现就像是六个不同的芯片一样。

制造:优势与挑战

在早几年的 IEEE IEDM 论坛上,三星的 Kinam Kim 发表了主题演讲,他预测到 2030 年将出现 1,000 层闪存。这可能听起来令人头晕,但这并不完全是科幻小说。Imec 存储内存项目总监 Maarten Rosmeulen 表示:“相对 NAND 闪存的历史趋势线而言,这一速度已经放缓。” “如果你看看其他公司,比如美光或西部数据,他们在公开声明中提出的内容,你会发现他们的速度甚至比这还要慢。不同制造商之间也存在一些差异——看起来他们正在延长路线图,让它放慢速度。我们相信这是因为维持这个空间的运转需要非常高的投资。”

尽管如此,竞争风险仍然足够高,这些投资是不可避免的。“前进的主要方式,主要的乘数,是在堆栈中添加更多层,”Rosmeulen 说。“几乎没有空间进行 XY 收缩并缩小内存空洞。这很难做到。也许他们会在这里或那里挤压百分之几,将孔放得更近,孔之间的缝隙更少等等。但这并不是最大的收益所在。如果你能继续堆叠更多的层,密度只能以目前的速度显着提高。”

图 2:NAND 制造中的 3D 步骤

除了整个过程的核心不可避免的问题之外,进一步堆叠似乎是合理的。

“主要挑战在于蚀刻,因为你必须蚀刻具有非常高深宽比的非常深的孔,”Rosmeulen 说。“如果你看看上一代的 128 层,这大约是一个 6、7 或 8 微米深的孔,直径仅为 120 纳米左右,具有极高的纵横比,或者可能更高一点,但并非如此很多。蚀刻技术取得了进步,可以一次性蚀刻更深的孔,但速度不会更快。您无法提高蚀刻速度。因此,如果工艺流程以沉积和蚀刻为主,并且这些工艺步骤没有提高成本效率,那么添加更多层就不再能够有效地降低成本。”

蚀刻也只是多个步骤之一。“除了蚀刻之外,您还需要用非常薄的介电层上下均匀地填充这个孔,”Synopsys 的 Lin 说。“通常,由于晶圆的化学性质,沉积几纳米的层并不容易。在这里,他们必须一路向下才能填满。有亚原子层沉积方法,但仍然具有挑战性。另一个巨大的挑战是压力。如果您构建了如此多的层并经历一些蚀刻/沉积/清洁/热循环,则可能会导致局部和全局应力。在局部,因为钻孔后,您需要在整个堆栈上切出一条非常深的沟槽。它变成了一座非常高的摩天大楼,而且摇摇欲坠。如果你开始进行一些清洗或其他过程,很多事情都可能发生,导致两座摩天大楼相互倒塌。那么你就失去了收益。通过将如此多的材料相互叠加并切割不同的图案,这可能会产生全局应力并导致晶圆翘曲,这将使其无法在晶圆厂中进行处理,因为晶圆必须是平坦的。

请记住,蚀刻是穿过不同材料层的。

Objective Analysis 的 Handy 表示,三星的解决方案是创建极薄的层。“这对整个行业很有用,因为每个人都使用几乎相同的工具来创建这些东西。”

结论

2016年,专家指出,由于技术问题,3D NAND可能会在300层或接近300层时失去动力。这似乎已被今天的谨慎乐观所取代。

“[SK Hynix 的 238 层之后]我预计未来几年层数将以大致相同的速度增加,”IBM 的 Pletka 表示。“然而,从技术角度来看,由于高深宽比蚀刻工艺,增加层数面临挑战,而且资本支出也面临挑战,因为制造芯片的时间随着层数的增加而增加。这就是为什么我们将看到新的缩放方向,通过制作更薄的层、横向缩放(例如更密集地放置垂直孔)以及使用更有效的布局(例如共享位线和逻辑缩放)(例如,使用分栅架构或存储更多每单元位数)。借助这些技术,预计 NAND 闪存的存储密度至少在未来 5 到 10 年内将继续以类似的速度增长。”

其他人也同意。Objective Analysis 首席分析师吉姆·汉迪 (Jim Handy) 表示:“当人们说我们无法超越这么多层时,这实际上是没有物理限制的。” “在半导体领域,总是有人说我们做不到。我们无法进行 20 纳米以下的光刻。现在,他们正在研究 1 纳米。三星谈到了 1,000 层。20年后,我们可能会嘲笑我们曾经认为这已经很多了。”

相关问答

内存 SDRAM和DDR,DDR2,DDR3有什么区别 - 张小满呢 的回答 - 懂得3、寻址时序(Timing)就像DDR2从DDR转变而来后延迟周期数增加一样,DDR3的CL周期也将比DDR2有所提高。DDR2的CL范围一般在2至5之间,而DDR3则在5至11...

内存 条镀金层厚度?镀金层的厚度在200um(微米)到500um(微米)之间,但也有个别产品可能会更厚或更薄。镀金层的厚度会影响到内存条的稳定性和性能,尤其是在高负载、高并发或高...

iqoo12pro参数配置-ZOL问答曼岛特别版更是搭配了绿色有机硅皮革搭配微米级玻璃纤维基材。iQOO11Pro是iQO...3GWLAN功能双频WiFi,WiFi6(IEEE802.11a/b/g/n/ac/ax),2x2MIMO...

AMD CPU右下角的N和T是什么意思-ZOL问答生产日期:其中第三四个数字代表第几周生产,M代表Monday(星期一),PM代表下午。通常说来,时间越往后的产品,bug越少,性能也越好。2.Duron编号格式:例如PGA封装...

目前最大容量的固态硬盘是哪家公司产的?现在INTELG3固件有个BUG,也就是所说的8MB门。以是照样镁光的M4吧。有钱就买打容量的,没钱的话64GB做个系统盘也够用了。镁光C400也可以或许或许。你要问最...

sim卡是 多少 纳米的芯片?SIM卡芯片的数据存储量并不大,晶体管数量也没电脑CPU这类恐怖,一般都是微米级别的工艺了,0.13微米的工艺了。纳米SIM卡是手机用的微型SIM卡,比Micro-SIM卡小...

DNA 多少微米 ?2000000微米也就是2米细胞中的DNA作为一种天然呈螺旋状的分子,在酶的作用下处于超螺旋状态,以节省存储空间。超螺旋状态可以理解为握住一条绳子一头,旋转另一...

小米mixfold配置怎么样?-小米MIX FOLD(12GB/256GB/5G版)问答-...[回答]折叠状态下,则是6.52英寸的柔性AMOLED屏幕,分辨率2520×840,刷新率90Hz,亮度700nitHBM,也支持杜比视界。小米MIXFOLD的价格为12GB+256GB9999元(黑色...

真我gtneo是ddr5 内存 吗?不是,都不是高通的,是天玑1200.真我GTNeo背面采用微米级光哑同体工艺,与AG磨砂工艺相比,颗粒感更强,不易沾染指纹。后置摄像头位置向下延伸出一条亮面,亮...

笔记本显存ddr3谁知道是什么意思?_其他问答_系统粉DDR5是极速内存,处理速度比DDR3更快。计算显存带宽的时候DDR3是乘以2,DDR5是乘以4.也就是说同样的显存频率下DDR5的显存带宽是DDR3的两倍。现在主流...