TMSC6678 EMIF BOOT介绍

这篇文章主要介绍C6678的EMIF16多核boot过程。

我们把应用程序烧写到flash,并实现dsp的自启动,包括四个部分:需要烧写的应用工程、转换工具、把转换后的文件烧写到dsp外挂的flash的烧写工程,以及Boot Mode pins管脚的配置。

1、Boot Mode pins管脚在EMIF boot模式下Boot Mode pins[5]应设置为1,其他位可以都设置为0.

Boot Mode pins

2、应用工程

在core0的应用工程中,除了完成自身的任务之外,还要作为主核去加载其他的核。就是core0需要把其他核的应用工程文件从flsah中读取到dsp的内存或者DDR中。所以在core0的应用工程中需要加上加载其他的核的程序模块。这个模块包含EMIF16接口初始化、Nor Flash初始化,以及Core0从Flash中读取其他核的代码到相应地址。

这就涉及到一个问题,Core0从Flash中读数据时,应该读取哪些数据、这些数据什么含义、把这些数据读取到哪些地址去。

应该读取哪些数据包含从哪个地址开始读,数据的长度。从哪个地址开始读:我们在烧写工程中设定了应用工程文件写到flash的地址,我们就从这个地址开始读。数据的长度,数据读取后存到的目的地址及数据,都在待烧写的文件中。待烧写的文件的格式如下:

所以我们需要转换工具把应用工程程序转换为具有这个格式的文件。

3、转换工具

转换工具实现将应用工程的.out文件转换成.bin文件。core0的应用工程必须转换,为了方便,可以将core1~core7有几份不同的应用工程就转换几份。

4、烧写工程

烧写工程是将转换后的文件烧写到Nor Flash的工程,只需core0运行。主要包括EMIF16接口初始化、Nor Flash初始化、待烧写文件的读取、Nor Flash的擦除和写入。可以程序自己读取待烧写文件的数据,也可以将待烧写文件通过CCS的load memory,将待烧写文件先读取到内存或者DDR中。

对于core0来说,其.bin文件是必须要烧写的,而且烧写地址固定为0x70000000。

对于其它核core1~core7,由于它们的待烧写代码的情况很多,比如有些核的代码相同,有些核的代码不同,相同代码就烧到同一块空间,不同代码烧到不同空间。

因为在启动的时候,需要知道从flash的哪个地址开始读,所以我们需要设定各个和的烧写文件写到flash中的地址。我们不妨给每一个设定一个写入的地址。为了简单方便,可以将core1~core7中相同的烧写文件(即同一个应用工程)都烧到预定义的核号最小的Flash空间。

然后断电重启,将CCS与C6678连接上之后,看PC指针的值,若PC指针的值在ROM里(0x20B00000到0x20B1FFFF),则说明加载不成功。若PC指针的值不在这个区间,则查看dsp的运行结果是否符合预期。

TI AM33525459 工业核心板硬件说明书

创龙科技SOM-TL335x-S是一款基于TI Sitara系列AM3352/AM3354/AM3359 ARM Cortex-A8高性能低功耗处理器设计的低成本工业级核心板,通过邮票孔连接方式引出千兆网口、LCD、GPMC等接口。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。典型应用领域分别为:通讯管理、数据采集、人机交互、运动控制、智能电力。

硬件资源

SOM-TL335x-S核心板板载CPU、ROM、RAM、晶振、电源管理芯片、LED等硬件资源,并通过邮票孔连接方式引出IO。

图 1 核心板硬件框图

图 2

核心板采用4x 40pin邮票孔连接方式,共160pin,引脚间距为1.0mm。

图 3

CPU

核心板CPU型号兼容AM3352BZCZD80/AM3354BZCZD80/AM3359BZCZA80,NFBGA(ZCZ)封装,工作温度为-40°C~90°C,引脚数量为324个,尺寸为15mm*15mm。

TI AM335x处理器架构如下:

表1

AM335x

1x ARM Cortex-A8,主频800MHz

1x PRU-ICSS,每个PRU-ICSS子系统含2个PRU(Programmable Real-time Unit)核,共4个PRU核(仅限AM3359)

1x SGX530 3D GPU图形加速器(仅限AM3354、AM3359)

图 4 AM335x处理器功能框图

ROM

1.2.1 eMMC/NAND FLASH

由于eMMC与NAND FLASH在PCB板上使用叠封装形式,因此核心板可选贴eMMC或NAND FLASH。

核心板通过MMC1总线连接工业级eMMC,采用4bit数据线,型号兼容SkyHigh Memory的S40FC004C1B1I00000(4GByte)、Micron的MTFC4GACAJCN-4M IT(4GByte)和Micron的MTFC8GAKAJCN-4M IT(8GByte)。由于MMC1信号与GPMC信号存在引脚复用关系,因此eMMC版本核心板无法使用GPMC功能。

核心板通过GPMC总线连接工业级NAND FLASH,片选引脚为GPMC_CSn0,采用8bit数据线,型号兼容SkyHigh Memory的S34ML04G2(512MByte)和JSC的JS27HU4G08SDN-25(512MByte)。

1.2.2 SPI FLASH

核心板通过SPI0总线连接工业级SPI FLASH,片选引脚为SPI0_CS0,型号为W25Q64JVSSIQ,容量为64Mbit。

备注:U8(W25Q64JVSSIQ)默认空贴。

图 5

RAM

核心板通过专用EMIF总线连接1片工业级DDR3,采用16bit数据线,型号兼容ISSI的IS43TR16128DL(256MByte)、ISSI的IS43TR16256BL(512MByte)、Micron的MT41K128M16(256MByte)和Micron的MT41K256M16(512MByte),支持DDR3-800工作模式(400MHz)。

晶振

核心板采用一个工业级晶振(OSC)为CPU提供系统时钟源,时钟频率为24MHz,精度为±20ppm。

电源

核心板采用专用的工业级PMIC电源管理芯片,满足系统的供电要求和CPU上电、掉电时序要求,采用5V直流电源供电。

LED

核心板板载三个LED。其中LED0为电源指示灯,系统上电后默认会点亮。LED1和LED2为用户可编程指示灯,分别对应GPIO3[7]和GPIO3[8]两个引脚,低电平点亮。

图 6

图 7

外设资源

核心板引出的主要外设资源及性能参数如下表所示。

表 1

外设资源

数量

性能参数

LCD

1

最高支持24bit像素位宽,兼容18bit、16bit和12bit;最高支持2048 x 2048分辨率;(像素时钟最大126MHz);

UART

6

最高支持波特率为3.6864Mbps;

支持硬件或软件流控;

DCAN

2

支持CAN 2.0B协议;

最高支持1Mbit/s速率;

SPI

2

每路SPI包含2个外部片选信号;

最高支持48MHz工作频率;

I2C

3

支持100KHz、400KHz速率;

Ethernet

2

支持10/100/1000兆网口配置;

支持网络自适应;

GPMC

1

支持7个片选信号;

最高支持100MHz工作主频;

最高支持27bit地址线、16bit数据线;

备注:GPMC信号与MMC1信号存在引脚复用关系,因此eMMC版本核心板无法使用GPMC功能;

McASP

2

最高支持4个通道;

支持以不同的速率接收和传输,如可在48KHz接收数据,在96KHz或192KHz上输出采样数据;

USB 2.0

2

支持DRD(即Host或Device)模式;

支持High-Speed/Full-Speed/Low-Speed模式;

MMC/SD/SDIO

3

支持1、4、8位MMC、SD和SDIO模式;

支持SD卡检测和写保护;

兼容MMC4.3、SDIO2.0标准;

备注:核心板板载eMMC设备已使用MMC1;

WDT

1

32bit定时器计数器;

可产生复位或中断信号,映射至ARM核;

NMI

1

映射至ARM核;

eHRPWM

3

最高支持6路PWM输出,每路PWM具有专用16位时基计数器(用于周期和频率控制);

工作频率10MHz,理论支持PWM周期为152Hz~10MHz;

eCAP

3

最高支持3路eCAP输入或PWM输出(不使用eCAP捕获模式时,可配置为PWM输出模式);

每路eCAP具有专用32位时基计数器;

eQEP

3

最高支持3路eQEP输入;

支持正交时钟模式和方向计数模式;

Timers

8

最高支持8路通用定时器;

每路定时器具有专用32bit定时计数器,支持自动重载模式;

可从系统时钟(25MHz)或32KHz时钟计时;

Timer1支持1ms的滴答时钟生成;

RTC

1

内部集成32.768KHz晶振;

支持报警中断、定时中断;

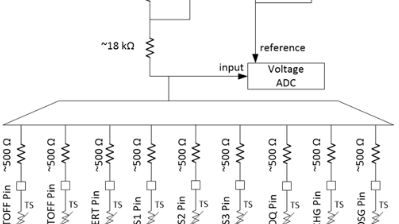

ADC

1

200KSPS采样率;

8通道输入,通过多路开关切换;

可配置为4线、5线、8线电阻触摸控制器;

JTAG

1

支持ARM和PRU调试;

支持器件边界扫描;

支持IEEE1500;

部分外设资源存在引脚复用情况,可在实际开发过程中使用TI PINMUX工具对外设资源进行合理分配,工具参考链接:http://processors.wiki.ti.com/index.php/TI_PinMux_Tool。

引脚说明

2.1 引脚排列

核心板邮票孔引脚采用4x 40pin规格,引脚排列如下图所示。

图 8

2.2 引脚定义

核心板引脚定义如下表。

其中“邮票孔引脚号”为核心板邮票孔引脚序列号,“芯片引脚号”为CPU引脚序列号,“引脚信号名称”为CPU引脚信号名称,“引脚功能”为核心板引脚推荐功能描述。

2.2.1 CON0A

表 2

邮票孔引脚号

芯片引脚号

引脚信号名称

引脚功能

参考电平

1

-

GND

GND

GND

2

R1

R1/LCD_DATA0/GPMC_A0/PR1_MII_MT0_CLK/EHRPWM2A/PRU1_R30[0]/PRU1_R31[0]/GPIO2[6]

LCDC

3.3V

3

R2

R2/LCD_DATA1/GPMC_A1/PR1_MII0_TXEN/EHRPWM2B/PRU1_R30[1]/PRU1_R31[1]/GPIO2[7]

LCDC

3.3V

4

R3

R3/LCD_DATA2/GPMC_A2/PR1_MII0_TXD3/EHRPWM2_TRIPZONE_INPUT/PRU1_R30[2]/PRU1_R31[2]/GPIO2[8]

LCDC

3.3V

5

R4

R4/LCD_DATA3/GPMC_A3/PR1_MII0_TXD2/EHRPWM0_SYNCO/PRU1_R30[3]/PRU1_R31[3]/GPIO2[9]

LCDC

3.3V

6

T1

T1/LCD_DATA4/GPMC_A4/PR1_MII0_TXD1/EQEP2A_IN/PRU1_R30[4]/PRU1_R31[4]/GPIO2[10]

LCDC

3.3V

7

T2

T2/LCD_DATA5/GPMC_A5/PR1_MII0_TXD0/EQEP2B_IN/PRU1_R30[5]/PRU1_R31[5]/GPIO2[11]

LCDC

3.3V

8

T3

T3/LCD_DATA6/GPMC_A6/PR1_EDIO_DATA_IN6/EQEP2_INDEX/PR1_EDIO_DATA_OUT6/PRU1_R30[6]/PRU1_R31[6]/GPIO2[12]

LCDC

3.3V

9

T4

T4/LCD_DATA7/GPMC_A7/PR1_EDIO_DATA_IN7/EQEP2_STROBE/PR1_EDIO_DATA_OUT7/PRU1_R30[7]/PRU1_R31[7]/GPIO2[13]

LCDC

3.3V

10

U1

U1/LCD_DATA8/GPMC_A12/EHRPWM1_TRIPZONE_INPUT/MCASP0_ACLKX/UART5_TXD/PR1_MII0_RXD3/UART2_CTSN/GPIO2[14]

LCDC

3.3V

11

U2

U2/LCD_DATA9/GPMC_A13/EHRPWM0_SYNCO/MCASP0_FSX/UART5_RXD/PR1_MII0_RXD2/UART2_RTSN/GPIO2[15]

LCDC

3.3V

12

U3

U3/LCD_DATA10/GPMC_A14/EHRPWM1A/MCASP0_AXR0/PR1_MII0_RXD1/UART3_CTSN/GPIO2[16]

LCDC

3.3V

13

U4

U4/LCD_DATA11/GPMC_A15/EHRPWM1B/MCASP0_AHCLKR/MCASP0_AXR2/PR1_MII0_RXD0/UART3_RTSN/GPIO2[17]

LCDC

3.3V

14

V2

V2/LCD_DATA12/GPMC_A16/EQEP1A_IN/MCASP0_ACLKR/MCASP0_AXR2/PR1_MII0_RXLINK/UART4_CTSN/GPIO0[8]

LCDC

3.3V

15

V3

V3/LCD_DATA13/GPMC_A17/EQEP1B_IN/MCASP0_FSR/MCASP0_AXR3/PR1_MII0_RXER/UART4_RTSN/GPIO0[9]

LCDC

3.3V

16

V4

V4/LCD_DATA14/GPMC_A18/EQEP1_INDEX/MCASP0_AXR1/UART5_RXD/PR1_MII_MR0_CLK/UART5_CTSN/GPIO0[10]

LCDC

3.3V

17

T5

T5/LCD_DATA15/GPMC_A19/EQEP1_STROBE/MCASP0_AHCLKX/MCASP0_AXR3/PR1_MII0_RXDV/UART5_RTSN/GPIO0[11]

LCDC

3.3V

18

-

GND

GND

GND

19

U5

U5/LCD_VSYNC/GPMC_A8/GPMC_A1/PR1_EDIO_DATA_IN2/PR1_EDIO_DATA_OUT2/PRU1_R30[8]/PRU1_R31[8]/GPIO2[22]

LCDC

3.3V

20

R5

R5/LCD_HSYNC/GPMC_A9/GPMC_A2/PR1_EDIO_DATA_IN3/PR1_EDIO_DATA_OUT3/PRU1_R30[9]/PRU1_R31[9]/GPIO2[23]

LCDC

3.3V

21

V5

V5/LCD_PCLK/GPMC_A10/PR1_MII0_CRS/PR1_EDIO_DATA_IN4/PR1_EDIO_DATA_OUT4/PRU1_R30[10]/PRU1_R31[10]/GPIO2[24]

LCDC

3.3V

22

R6

R6/LCD_AC_BIAS_EN/GPMC_A11/PR1_MII1_CRS/PR1_EDIO_DATA_IN5/PR1_EDIO_DATA_OUT5/PRU1_R30[11]/PRU1_R31[11]/GPIO2[25]

LCDC

3.3V

23

U10

U10/GPMC_AD8/LCD_DATA23/MMC1_DAT0/MMC2_DAT4/EHRPWM2A/PR1_MII_MT0_CLK/GPIO0[22]

GPMC

3.3V

24

T10

T10/GPMC_AD9/LCD_DATA22/MMC1_DAT1/MMC2_DAT5/EHRPWM2B/PR1_MII0_COL/GPIO0[23]

GPMC

3.3V

25

T11

T11/GPMC_AD10/LCD_DATA21/MMC1_DAT2/MMC2_DAT6/EHRPWM2_TRIPZONE_INPUT/PR1_MII0_TXEN/GPIO0[26]

GPMC

3.3V

26

U12

U12/GPMC_AD11/LCD_DATA20/MMC1_DAT3/MMC2_DAT7/EHRPWM0_SYNCO/PR1_MII0_TXD3/GPIO0[27]

GPMC

3.3V

27

T12

T12/GPMC_AD12/LCD_DATA19/MMC1_DAT4/MMC2_DAT0/EQEP2A_IN/PR1_MII0_TXD2/PRU0_R30[14]/GPIO1[12]

GPMC

3.3V

28

R12

R12/GPMC_AD13/LCD_DATA18/MMC1_DAT5/MMC2_DAT1/EQEP2B_IN/PR1_MII0_TXD1/PRU0_R30[15]/GPIO1[13]

GPMC

3.3V

29

V13

V13/GPMC_AD14/LCD_DATA17/MMC1_DAT6/MMC2_DAT2/EQEP2_INDEX/PR1_MII0_TXD0/PRU0_R31[14]/GPIO1[14]

GPMC

3.3V

30

U13

U13/GPMC_AD15/LCD_DATA16/MMC1_DAT7/MMC2_DAT3/EQEP2_STROBE/PR1_ECAP0_PWM/PRU0_R31[15]/GPIO1[15]

GPMC

3.3V

31

-

GND

GND

GND

32

T9

T9/GPMC_AD7/MMC1_DAT7/GPIO1[7]

GPMC

3.3V

33

R9

R9/GPMC_AD6/MMC1_DAT6/GPIO1[6]

GPMC

3.3V

34

V8

V8/GPMC_AD5/MMC1_DAT5/GPIO1[5]

GPMC

3.3V

35

U8

U8/GPMC_AD4/MMC1_DAT4/GPIO1[4]

GPMC

3.3V

36

T8

T8/GPMC_AD3/MMC1_DAT3/GPIO1[3]

GPMC

3.3V

37

R8

R8/GPMC_AD2/MMC1_DAT2/GPIO1[2]

GPMC

3.3V

38

V7

V7/GPMC_AD1/MMC1_DAT1/GPIO1[1]

GPMC

3.3V

39

U7

U7/GPMC_AD0/MMC1_DAT0/GPIO1[0]

GPMC

3.3V

40

-

GND

GND

GND

2.2.2 CON0B

表 3

邮票孔引脚号

芯片引脚号

引脚信号名称

引脚功能

参考电平

41

-

GND

GND

GND

42

U9

U9/GPMC_CSN1/MMC1_CLK/GPIO1[30]

GPMC

3.3V

43

V9

V9/GPMC_CSN2/MMC1_CMD/GPIO1[31]

GPMC

3.3V

44

T13

T13/GPMC_CSN3/GPMC_A3/RMII2_CRS_DV/MMC2_CMD/PR1_MII0_CRS/PR1_MDIO_DATA/EMU4/GPIO2[0]

GPMC

3.3V

45

T7

T7/GPMC_OEN_REN/TIMER7/GPIO2[3]

GPMC

3.3V

46

U6

U6/GPMC_WEN/TIMER6/GPIO2[4]

GPMC

3.3V

47

R7

R7/GPMC_ADVN_ALE/TIMER4/GPIO2[2]

GPMC

3.3V

48

T6

T6/GPMC_BE0N_CLE/TIMER5/GPIO2[5]

GPMC

3.3V

49

U18

U18/GPMC_BE1N/GMII2_COL/GPMC_CSN6/MMC2_DAT3/GPMC_DIR/PR1_MII1_RXLINK/MCASP0_ACLKR/GPIO1[28]

GPIO

3.3V

50

T17

T17/GPMC_WAIT0/GMII2_CRS/GPMC_CSN4/RMII2_CRS_DV/MMC1_SDCD/PR1_MII1_COL/UART4_RXD/GPIO0[30]

GPMC

3.3V

51

V12

V12/GPMC_CLK/LCD_MEMORY_CLK/GPMC_WAIT1/MMC2_CLK/PR1_MII1_CRS/PR1_MDIO_MDCLK/MCASP0_FSR/GPIO2[1]

GPIO

3.3V

52

R13

R13/GPMC_A0/GMII2_TXEN/RGMII2_TCTL/RMII2_TXEN/GPMC_A16/PR1_MII_MT1_CLK/EHRPWM1_TRIPZONE_INPUT/GPIO1[16]

RGMII2

3.3V

53

V14

V14/GPMC_A1/GMII2_RXDV/RGMII2_RCTL/MMC2_DAT0/GPMC_A17/PR1_MII1_TXD3/EHRPWM0_SYNCO/GPIO1[17]

RGMII2

3.3V

54

U14

U14/GPMC_A2/GMII2_TXD3/RGMII2_TD3/MMC2_DAT1/GPMC_A18/PR1_MII1_TXD2/EHRPWM1A/GPIO1[18]

RGMII2

3.3V

55

T14

T14/GPMC_A3/GMII2_TXD2/RGMII2_TD2/MMC2_DAT2/GPMC_A19/PR1_MII1_TXD1/EHRPWM1B/GPIO1[19]

RGMII2

3.3V

56

R14

R14/GPMC_A4/GMII2_TXD1/RGMII2_TD1/RMII2_TXD1/GPMC_A20/PR1_MII1_TXD0/EQEP1A_IN/GPIO1[20]

RGMII2

3.3V

57

V15

V15/GPMC_A5/GMII2_TXD0/RGMII2_TD0/RMII2_TXD0/GPMC_A21/PR1_MII1_RXD3/EQEP1B_IN/GPIO1[21]

RGMII2

3.3V

58

U15

U15/GPMC_A6/GMII2_TXCLK/RGMII2_TCLK/MMC2_DAT4/GPMC_A22/PR1_MII1_RXD2/EQEP1_INDEX/GPIO1[22]

RGMII2

3.3V

59

T15

T15/GPMC_A7/GMII2_RXCLK/RGMII2_RCLK/MMC2_DAT5/GPMC_A23/PR1_MII1_RXD1/EQEP1_STROBE/GPIO1[23]

RGMII2

3.3V

60

V16

V16/GPMC_A8/GMII2_RXD3/RGMII2_RD3/MMC2_DAT6/GPMC_A24/PR1_MII1_RXD0/MCASP0_ACLKX/GPIO1[24]

RGMII2

3.3V

61

U16

U16/GPMC_A9/GMII2_RXD2/RGMII2_RD2/MMC2_DAT7/GPMC_A25/PR1_MII_MR1_CLK/MCASP0_FSX/GPIO1[25]

RGMII2

3.3V

62

T16

T16/GPMC_A10/GMII2_RXD1/RGMII2_RD1/RMII2_RXD1/GPMC_A26/PR1_MII1_RXDV/MCASP0_AXR0/GPIO1[26]

RGMII2

3.3V

63

V17

V17/GPMC_A11/GMII2_RXD0/RGMII2_RD0/RMII2_RXD0/GPMC_A27/PR1_MII1_RXER/MCASP0_AXR1/GPIO1[27]

RGMII2

3.3V

64

B18

B18/NNMI

nNMI

3.3V

65

-

NC

-

-

66

-

NC

-

-

67

U17

U17/GPMC_WPN/GMII2_RXER/GPMC_CSN5/RMII2_RXER/MMC2_SDCD/PR1_MII1_TXEN/UART4_TXD/GPIO0[31]

GPIO

3.3V

68

C5

C5/EXT_WAKEUP

EXT_WAKEUP

1.8V

69

C11

C11/TMS

JTAG

3.3V

70

B11

B11/TDI

JTAG

3.3V

71

B10

B10/TRSTN

JTAG

3.3V

72

A11

A11/TDO

JTAG

3.3V

73

A12

A12/TCK

JTAG

3.3V

74

-

PMIC_PB_IN

PMIC POWERON

5V

75

-

VDD_5V_MAIN

5V Power Input

Power

76

-

VDD_5V_MAIN

5V Power Input

Power

77

-

GND

GND

GND

78

-

GND

GND

GND

79

-

RESETn_IN

Reset Input

3.3V

80

-

VDD_3V3_VAUX2

3.3V Power Output

Power

2.2.3 CON0C

表 4

邮票孔引脚号

芯片引脚号

引脚信号名称

引脚功能

参考电平

81

-

GND

GND

GND

82

R17

R17/USB1_DP

USB1

-

83

R18

R18/USB1_DM

USB1

-

84

-

GND

GND

GND

85

T18

T18/USB1_VBUS(USB1_VBUS_5V)

USB1

5V

86

P17

P17/USB1_ID

USB1

1.8V

87

F15

F15/USB1_DRVVBUS/GPIO3[13]

USB1

3.3V

88

-

GND

GND

GND

89

N17

N17/USB0_DP

USB0

-

90

N18

N18/USB0_DM

USB0

-

91

-

GND

GND

GND

92

P15

P15/USB0_VBUS(USB0_VBUS)

USB0

5V

93

P16

P16/USB0_ID

USB0

1.8V

94

F16

F16/USB0_DRVVBUS/GPIO0[18]

USB0

3.3V

95

-

GND

GND

GND

96

M17

M17/MDIO_DATA/TIMER6/UART5_RXD/UART3_CTSN/MMC0_SDCD/MMC1_CMD/MMC2_CMD/GPIO0[0]

MDIO

3.3V

97

M18

M18/MDIO_CLK/TIMER5/UART5_TXD/UART3_RTSN/MMC0_SDWP/MMC1_CLK/MMC2_CLK/GPIO0[1]

MDIO

3.3V

98

M16

M16/GMII1_RXD0/RMII1_RXD0/RGMII1_RD0/MCASP1_AHCLKX/MCASP1_AHCLKR/MCASP1_ACLKR/MCASP0_AXR3/GPIO2[21]

RGMII1

3.3V

99

L15

L15/GMII1_RXD1/RMII1_RXD1/RGMII1_RD1/MCASP1_AXR3/MCASP1_FSR/EQEP0_STROBE/MMC2_CLK/GPIO2[20]

RGMII1

3.3V

100

L16

L16/GMII1_RXD2/UART3_TXD/RGMII1_RD2/MMC0_DAT4/MMC1_DAT3/UART1_RIN/MCASP0_AXR1/GPIO2[19]

RGMII1

3.3V

101

L17

L17/GMII1_RXD3/UART3_RXD/RGMII1_RD3/MMC0_DAT5/MMC1_DAT2/UART1_DTRN/MCASP0_AXR0/GPIO2[18]

RGMII1

3.3V

102

L18

L18/GMII1_RXCLK/UART2_TXD/RGMII1_RCLK/MMC0_DAT6/MMC1_DAT1/UART1_DSRN/MCASP0_FSX/GPIO3[10]

RGMII1

3.3V

103

J17

J17/GMII1_RXDV/LCD_MEMORY_CLK/RGMII1_RCTL/UART5_TXD/MCASP1_ACLKX/MMC2_DAT0/MCASP0_ACLKR/GPIO3[4]

RGMII1

3.3V

104

K17

K17/GMII1_TXD0/RMII1_TXD0/RGMII1_TD0/MCASP1_AXR2/MCASP1_ACLKR/EQEP0B_IN/MMC1_CLK/GPIO0[28]

RGMII1

3.3V

105

K16

K16/GMII1_TXD1/RMII1_TXD1/RGMII1_TD1/MCASP1_FSR/MCASP1_AXR1/EQEP0A_IN/MMC1_CMD/GPIO0[21]

RGMII1

3.3V

106

K15

K15/GMII1_TXD2/DCAN0_RX/RGMII1_TD2/UART4_TXD/MCASP1_AXR0/MMC2_DAT2/MCASP0_AHCLKX/GPIO0[17]

RGMII1

3.3V

107

J18

J18/GMII1_TXD3/DCAN0_TX/RGMII1_TD3/UART4_RXD/MCASP1_FSX/MMC2_DAT1/MCASP0_FSR/GPIO0[16]

RGMII1

3.3V

108

K18

K18/GMII1_TXCLK/UART2_RXD/RGMII1_TCLK/MMC0_DAT7/MMC1_DAT0/UART1_DCDN/MCASP0_ACLKX/GPIO3[9]

RGMII1

3.3V

109

J16

J16/GMII1_TXEN/RMII1_TXEN/RGMII1_TCTL/TIMER4/MCASP1_AXR0/EQEP0_INDEX/MMC2_CMD/GPIO3[3]

RGMII1

3.3V

110

-

GND

GND

GND

111

F17

F17/MMC0_DAT3/GPMC_A20/UART4_CTSN/TIMER5/UART1_DCDN/PRU0_R30[8]/PRU0_R31[8]/GPIO2[26]

MMC0

3.3V

112

F18

F18/MMC0_DAT2/GPMC_A21/UART4_RTSN/TIMER6/UART1_DSRN/PRU0_R30[9]/PRU0_R31[9]/GPIO2[27]

MMC0

3.3V

113

G15

G15/MMC0_DAT1/GPMC_A22/UART5_CTSN/UART3_RXD/UART1_DTRN/PRU0_R30[10]/PRU0_R31[10]/GPIO2[28]

MMC0

3.3V

114

G16

G16/MMC0_DAT0/GPMC_A23/UART5_RTSN/UART3_TXD/UART1_RIN/PRU0_R30[11]/PRU0_R31[11]/GPIO2[29]

MMC0

3.3V

115

G17

G17/MMC0_CLK/GPMC_A24/UART3_CTSN/UART2_RXD/DCAN1_TX/PRU0_R30[12]/PRU0_R31[12]/GPIO2[30]

MMC0

3.3V

116

G18

G18/MMC0_CMD/GPMC_A25/UART3_RTSN/UART2_TXD/DCAN1_RX/PRU0_R30[13]/PRU0_R31[13]/GPIO2[31]

MMC0

3.3V

117

-

SYS_RESETn

Reset Output

3.3V

118

C15

C15/SPI0_CS1/UART3_RXD/ECAP1_IN_PWM1_OUT/MMC0_POW/XDMA_EVENT_INTR2/MMC0_SDCD/EMU4/GPIO0[6]

UART3

3.3V

119

C18

C18/ECAP0_IN_PWM0_OUT/UART3_TXD/SPI1_CS1/PR1_ECAP0_APWM/SPI1_SCLK/MMC0_SDWP/XDMA_EVENT_INTR2/GPIO0[7]

UART3

3.3V

120

-

GND

GND

GND

2.2.4 CON0D

表 5

邮票孔引脚号

芯片引脚号

引脚信号名称

引脚功能

参考电平

121

-

GND

GND

GND

122

H17

H17/GMII1_CRS/RMII1_CRS_DV/SPI1_D0/I2C1_SDA/MCASP1_ACLKX/UART5_CTSN/UART2_RXD/GPIO3[1]

SPI1

3.3V

123

J15

J15/GMII1_RXER/RMII1_RXER/SPI1_D1/I2C1_SCL/MCASP1_FSX/UART5_RTSN/UART2_TXD/GPIO3[2]

SPI1

3.3V

124

E15

E15/UART0_RXD/SPI1_CS0/DCAN0_TX/I2C2_SDA/ECAP2_IN_PWM2_OUT/PRU1_R30[14]/PRU1_R31[14]/GPIO1[10]

UART0

3.3V

125

E16

E16/UART0_TXD/SPI1_CS1/DCAN0_RX/I2C2_SCL/ECAP1_IN_PWM1_OUT/PRU1_R30[15]/PRU1_R31[15]/GPIO1[11]

UART0

3.3V

126

H16

H16/GMII1_COL/RMII2_REFCLK/SPI1_SCLK/UART5_RXD/MCASP1_AXR2/MMC2_DAT3/MCASP0_AXR2/GPIO3[0]

SPI1

3.3V

127

H18

H18/RMII1_REFCLK/XDMA_EVENT_INTR2/SPI1_CS0/UART5_TXD/MCASP1_AXR3/MMC0_POW/MCASP1_AHCLKX/GPIO0[29]

GPIO

3.3V

128

E18

E18/UART0_CTSN/UART4_RXD/DCAN1_TX/I2C1_SDA/SPI1_D0/TIMER7/PR1_EDC_SYNC0_OUT/GPIO1[8]

I2C1

3.3V

129

E17

E17/UART0_RTSN/UART4_TXD/DCAN1_RX/I2C1_SCL/SPI1_D1/SPI1_CS0/PR1_EDC_SYNC1_OUT/GPIO1[9]

I2C1

3.3V

130

C17

C17/I2C0_SDA/TIMER4/UART2_CTSN/ECAP2_IN_PWM2_OUT/GPIO3[5]

I2C0

3.3V

131

C16

C16/I2C0_SCL/TIMER7/UART2_RTSN/ECAP1_IN_PWM1_OUT/GPIO3[6]

I2C0

3.3V

132

D18

D18/UART1_CTSN/TIMER6/DCAN0_TX/I2C2_SDA/SPI1_CS0/PR1_UART0_CTS_N/PR1_EDC_LATCH0_IN/GPIO0[12]

DCAN0

3.3V

133

D17

D17/UART1_RTSN/TIMER5/DCAN0_RX/I2C2_SCL/SPI1_CS1/PR1_UART0_RTS_N/PR1_EDC_LATCH1_IN/GPIO0[13]

DCAN0

3.3V

134

D16

D16/UART1_RXD/MMC1_SDWP/DCAN1_TX/I2C1_SDA/PR1_UART0_RXD/PRU1_R31[16]/GPIO0[14]

UART1

3.3V

135

D15

D15/UART1_TXD/MMC2_SDWP/DCAN1_RX/I2C1_SCL/PR1_UART0_TXD/PRU0_R31[16]/GPIO0[15]

UART1

3.3V

136

A17

A17/SPI0_SCLK/UART2_RXD/I2C2_SDA/EHRPWM0A/PR1_UART0_CTS_N/PR1_EDIO_SOF/EMU2/GPIO0[2]

SPI0

3.3V

137

B17

B17/SPI0_D0/UART2_TXD/I2C2_SCL/EHRPWM0B/PR1_UART0_RTS_N/PR1_EDIO_LATCH_IN/EMU3/GPIO0[3]

SPI0

3.3V

138

B16

B16/SPI0_D1/MMC1_SDWP/I2C1_SDA/EHRPWM0_TRIPZONE_INPUT/PR1_UART0_RXD/PR1_EDIO_DATA_IN0/PR1_EDIO_DATA_OUT0/GPIO0[4]

SPI0

3.3V

139

-

NC

-

-

140

A15

A15/XDMA_EVENT_INTR0/TIMER4/CLKOUT1/SPI1_CS1/PRU1_R31[16]/EMU2/GPIO0[19]

GPIO

3.3V

141

D14

D14/XDMA_EVENT_INTR1/TCLKIN/CLKOUT2/TIMER7/PRU0_R31[16]/EMU3/GPIO0[20]

GPIO

3.3V

142

-

GND

GND

GND

143

A13

A13/MCASP0_ACLKX/EHRPWM0A/SPI1_SCLK/MMC0_SDCD/PRU0_R30[0]/PRU0_R31[0]/GPIO3[14]

McASP0

3.3V

144

B13

B13/MCASP0_FSX/EHRPWM0B/SPI1_D0/MMC1_SDCD/PRU0_R30[1]/PRU0_R31[1]/GPIO3[15]

McASP0

3.3V

145

D12

D12/MCASP0_AXR0/EHRPWM0_TRIPZONE_INPUT/SPI1_D1/MMC2_SDCD/PRU0_R30[2]/PRU0_R31[2]/GPIO3[16]

GPIO

3.3V

146

C12

C12/MCASP0_AHCLKR/EHRPWM0_SYNCI/MCASP0_AXR2/SPI1_CS0/ECAP2_IN_PWM2_OUT/PRU0_R30[3]/PRU0_R31[3]/GPIO3[17]

GPIO

3.3V

147

B12

B12/MCASP0_ACLKR/EQEP0A_IN/MCASP0_AXR2/MCASP1_ACLKX/MMC0_SDWP/PRU0_R30[4]/PRU0_R31[4]/GPIO3[18]

McASP0

3.3V

148

C13

C13/MCASP0_FSR/EQEP0B_IN/MCASP0_AXR3/MCASP1_FSX/EMU2/PRU0_R30[5]/PRU0_R31[5]/GPIO3[19]

McASP0

3.3V

149

D13

D13/MCASP0_AXR1/EQEP0_INDEX/MCASP1_AXR0/EMU3/PRU0_R30[6]/PRU0_R31[6]/GPIO3[20]

GPIO

3.3V

150

A14

A14/MCASP0_AHCLKX/EQEP0_STROBE/MCASP0_AXR3/MCASP1_AXR1/EMU4/PRU0_R30[7]/PRU0_R31[7]/GPIO3[21]

McASP0

3.3V

151

-

GND

GND

GND

152

C9

C9/AIN7

ADC

1.8V

153

A8

A8/AIN6

ADC

1.8V

154

B8

B8/AIN5

ADC

1.8V

155

C8

C8/AIN4

ADC

1.8V

156

A7

A7/AIN3

ADC

1.8V

157

B7

B7/AIN2

ADC

1.8V

158

C7

C7/AIN1

ADC

1.8V

159

B6

B6/AIN0

ADC

1.8V

160

-

GND_ADC

AGND

AGND

2.3 内部引脚说明

“邮票孔引脚号”NC表示核心板该内部引脚未引出到邮票孔,其他代表内部已使用且同时引出到核心板邮票孔。“芯片引脚号”为CPU引脚序列号,“引脚信号名称”为CPU引脚信号名称,“引脚功能”为核心板引脚推荐功能描述。

表 6

邮票孔引脚号

芯片引脚号

引脚信号名称

引脚功能

参考电平

NC

V10

XTALIN

OSC(Y1)

1.8V

NC

U11

XTALOUT

OSC(Y1)

1.8V

32

T9

T9/GPMC_AD7/MMC1_DAT7/GPIO1[7]

NAND FLASH

3.3V

33

R9

R9/GPMC_AD6/MMC1_DAT6/GPIO1[6]

3.3V

34

V8

V8/GPMC_AD5/MMC1_DAT5/GPIO1[5]

3.3V

35

U8

U8/GPMC_AD4/MMC1_DAT4/GPIO1[4]

3.3V

36

T8

T8/GPMC_AD3/MMC1_DAT3/GPIO1[3]

eMMC/NAND FLASH

3.3V

37

R8

R8/GPMC_AD2/MMC1_DAT2/GPIO1[2]

3.3V

38

V7

V7/GPMC_AD1/MMC1_DAT1/GPIO1[1]

3.3V

39

U7

U7/GPMC_AD0/MMC1_DAT0/GPIO1[0]

3.3V

42

U9

U9/GPMC_CSN1/MMC1_CLK/GPIO1[30]

eMMC

3.3V

43

V9

V9/GPMC_CSN2/MMC1_CMD/GPIO1[31]

3.3V

46

U6

U6/GPMC_WEN/TIMER6/GPIO2[4]

NAND FLASH

3.3V

47

R7

R7/GPMC_ADVN_ALE/TIMER4/GPIO2[2]

3.3V

48

T6

T6/GPMC_BE0N_CLE/TIMER5/GPIO2[5]

3.3V

45

T7

T7/GPMC_OEN_REN/TIMER7/GPIO2[3]

3.3V

50

T17

T17/GPMC_WAIT0/GMII2_CRS/GPMC_CSN4/

RMII2_CRS_DV/MMC1_SDCD/PR1_MII1_COL

/UART4_RXD/GPIO0[30]

3.3V

66

V6

V6/GPMC_CSN0/GPIO1[29]

3.3V

87

F15

F15/USB1_DRVVBUS/GPIO3[13]

USB1/PMIC SLEEP

3.3V

117

-

SYS_RESETn

Reset Output

3.3V

118

C15

C15/SPI0_CS1/UART3_RXD/ECAP1_IN_PWM1_OUT

/MMC0_POW/XDMA_EVENT_INTR2

/MMC0_SDCD/EMU4/GPIO0[6]

UART3

3.3V

130

C17

C17/I2C0_SDA/TIMER4/UART2_CTSN

/ECAP2_IN_PWM2_OUT/GPIO3[5]

PMIC

3.3V

131

C16

C16/I2C0_SCL/TIMER7/UART2_RTSN/

ECAP1_IN_PWM1_OUT/GPIO3[6]

PMIC

3.3V

136

A17

A17/SPI0_SCLK/UART2_RXD/I2C2_SDA

/EHRPWM0A/PR1_UART0_CTS_N/PR1_EDIO_SOF/EMU2/GPIO0[2]

SPI FLASH

3.3V

137

B17

B17/SPI0_D0/UART2_TXD/I2C2_SCL/EHRPWM0B/PR1_UART0_RTS_N/PR1_EDIO_LATCH_IN/EMU3/GPIO0[3]

3.3V

138

B16

B16/SPI0_D1/MMC1_SDWP/I2C1_SDA/EHRPWM0_TRIPZONE_INPUT/PR1_UART0_RXD/PR1_EDIO_DATA_IN0/PR1_EDIO_DATA_OUT0/GPIO0[4]

3.3V

NC

A16

A16/SPI0_CS0/MMC2_SDWP/I2C1_SCL/EHRPWM0_SYNCI/PR1_UART0_TXD/PR1_EDIO_DATA_IN1/PR1_EDIO_DATA_OUT1/GPIO0[5]

3.3V

补充说明:

EMU0/GPIO3[7]、EMU1/GPIO3[8]引脚分别连接核心板LED1和LED2,不通过邮票孔连接方式引出。JTAG的基本仿真功能无须使用此两个引脚。

图 9

由于I2C0已连接核心板PMIC电源管理芯片,同时也连接到底板的RTC时钟电路上使用,从系统稳定性角度考虑,建议进行底板设计时尽量选用其他I2C总线。

图 10

SPI0总线的SPI0_CS0(A16)片选引脚在核心板内部已被SPI FLASH使用,同时SPI0_CS0未引出核心板邮票孔管脚。若使用含SPI FLASH的核心板,邮票孔第136~138引脚只能作为SPI功能。

2.4 引脚上下拉说明

下表为核心板内部已作上下拉配置引脚的说明。表中未说明的引脚,核心板内部默认未作上下拉配置,直接通过邮票孔连接方式引出。

表 7

邮票孔引脚号

芯片引脚号

引脚信号名称

上下拉配置

上下拉电阻值

79

-

RESETn_IN

上拉3.3V

100K

117

-

SYS_RESETn

上拉3.3V

10K

68

C5

C5/EXT_WAKEUP

上拉1.8V

10K

131

C16

C16/I2C0_SCL

上拉3.3V

4K7

130

C17

C17/I2C0_SDA

上拉3.3V

4K7

17

T5

T5/LCD_DATA15/GPIO0[11]

下拉

10K

16

V4

V4/LCD_DATA14/GPIO0[10]

上拉3.3V

10K

15

V3

V3/LCD_DATA13/GPIO0[9]

下拉

10K

14

V2

V2/LCD_DATA12/GPIO0[8]

下拉

10K

13

U4

U4/LCD_DATA11/GPIO2[17]

下拉

10K

12

U3

U3/LCD_DATA10/GPIO2[16]

下拉

10K

11

U2

U2/LCD_DATA9/GPIO2[15]

上拉3.3V

10K

10

U1

U1/LCD_DATA8/GPIO2[14]

下拉

10K

9

T4

T4/LCD_DATA7/GPIO2[13]

上拉3.3V

10K

8

T3

T3/LCD_DATA6/GPIO2[12]

上拉3.3V

10K

7

T2

T2/LCD_DATA5/GPIO2[11]

上拉3.3V

10K

6

T1

T1/LCD_DATA4/GPIO2[10]

上拉3.3V

100K

5

R4

R4/LCD_DATA3/GPIO2[9]

上拉3.3V

100K

4

R3

R3/LCD_DATA2/GPIO2[8]

上拉3.3V

100K

3

R2

R2/LCD_DATA1/GPIO2[7]

上拉3.3V

100K

2

R1

R1/LCD_DATA0/GPIO2[6]

上拉3.3V

100K

39

U7

U7/GPMC_AD0/MMC1_DAT0

上拉3.3V

49K9

38

V7

V7/GPMC_AD1/MMC1_DAT1

上拉3.3V

49K9

37

R8

R8/GPMC_AD2/MMC1_DAT2

上拉3.3V

49K9

36

T8

T8/GPMC_AD3/MMC1_DAT3

上拉3.3V

49K9

35

V9

V9/GPMC_CSN2/MMC1_CMD

上拉3.3V

10K

64

B18

B18/nNMI

上拉3.3V

10K

139

A16

A16/SPI0_CS0/GPIO0[5]

上拉3.3V

10K

电气特性

3.1 工作环境

表 8

环境参数

最小值

典型值

最大值

工作温度

-40°C

/

85°C

存储温度

-50°C

/

90°C

工作湿度

35%(无凝露)

/

75%(无凝露)

存储湿度

35%(无凝露)

/

75%(无凝露)

工作电压

/

5.0V

/

3.2 功耗测试

工作状态

电压典型值

电流典型值

功耗典型值

状态1

5.0V

0.14A

0.70W

状态2

5.0V

0.22A

1.10W

备注:功耗基于TL335x-EVM-S评估板测得。功耗测试数据与具体应用场景有关,测试数据仅供参考。

状态1: 系统启动,评估板不接入外接模块,不执行额外应用程序。

状态2: 系统启动,评估板不接入外接模块,运行DDR压力读写测试程序,ARM Cortex-A8核心的资源使用率约为100%。

3.3 热成像图

核心板在常温环境下稳定工作10min后,测试核心板热成像图如下所示。H为最高温度,S为平均温度,最高温度是CPU(U4)。

备注:不同测试条件下结果会有所差异,数据仅供参考。

图 11

请参考以上测试结果,并根据实际情况合理选择散热方式。

机械尺寸

表 9

PCB尺寸

45mm*45mm

PCB层数

8层

元器件最高高度

1.28mm

PCB板厚

1.3mm

图 12

图 13

图 14

元器件最高高度:指核心板最高元器件水平面与PCB正面水平面的高度差。核心板最高元器件为CPU(U4)。

备注:若贴上SPI FLASH,则最高元器件为SPI FLASH,高度为2.2mm。

底板设计注意事项

5.1最小系统设计

基于SOM-TL335x-S核心板进行底板设计时,请务必满足最小系统设计要求,具体如下。

电源设计说明

(1)VDD_5V_SOM

VDD_5V_SOM为核心板的主供电输入,电源功率建议参考评估板按最大5W进行设计。

图 15

VDD_5V_SOM在核心板内部未预留总电源输入的储能大电容,底板设计时请参照评估板原理图,在靠近邮票孔焊盘位置放置储能大电容。

(2)VDD_3V3_MAIN

VDD_3V3_MAIN为底板提供的外设电源。为使VDD_3V3_MAIN满足处理器的上电、掉电时序要求,推荐使用VDD_3V3_VAUX2电源来控制VDD_3V3_MAIN的电源使能。

图 16

(3)VDD_3V3_VAUX2

VDD_3V3_VAUX2为核心板输出的BOOT SET配置专用供电电源,最大电流为100mA,请勿用于其他负载供电。

图 17

系统启动配置

由于BOOT SET引脚与LCDC(LCD Controller)信号存在复用关系,若使用LCDC信号外接设备(例如接LCD显示屏),请保证AM335x在上电初始化过程中BOOT SET引脚电平不受外接设备的影响,否则将会导致AM335x无法正常启动。

核心板内部BOOT[15:5]的已进行上下拉配置,BOOT[4:0]均已设计100K上拉电阻,具体如下图所示。设计系统启动配置电路时,请参考评估底板BOOT SET部分电路进行相关设计。

图 18

系统复位信号

(1)SYS_RESETn

SYS_RESETn为AM335x的WARM RESET复位输出引脚,可用于控制外设的复位。对于有严格上电复位顺序的外设,需要结合外设的上电和复位时序来使用SYS_RESETn。

(2)RESETn_IN

RESETn_IN为AM335x的WARM RESET复位输入引脚,RESETn_IN与SYS_RESETn通过100R电阻串接;核心板内部WARM RESET已设计10K上拉电阻,不使用RESETn_IN时请悬空处理。(备注:WARM RESET可做输入和输出。)

(3)PB_IN

PB_IN为PMIC的复位按钮输入引脚,PB_IN在PMIC内部已上拉100K到5V,默认情况可悬空处理。

(4)nNMI

nNMI为非屏蔽中断引脚,核心板内部已设计上拉电阻,默认情况可悬空处理。

5.2 功能引脚信号走线长度与阻抗说明

如下为核心板MDIO、RGMII、USB、GPMC、LCDC(LCD Controller)等功能引脚信号PCB走线长度与阻抗说明。

表 10

芯片引脚号

引脚信号名称

引脚功能

走线长度/mil

阻抗说明

R1

R1/LCD_DATA0/GPMC_A0/PR1_MII_MT0_CLK/EHRPWM2A/PRU1_R30[0]/PRU1_R31[0]/GPIO2[6]

LCDC

1677.68

单端50ohm

R2

R2/LCD_DATA1/GPMC_A1/PR1_MII0_TXEN/EHRPWM2B/PRU1_R30[1]/PRU1_R31[1]/GPIO2[7]

LCDC

1624.71

单端50ohm

R3

R3/LCD_DATA2/GPMC_A2/PR1_MII0_TXD3/EHRPWM2_TRIPZONE_INPUT/PRU1_R30[2]/PRU1_R31[2]/GPIO2[8]

LCDC

1491.31

单端50ohm

R4

R4/LCD_DATA3/GPMC_A3/PR1_MII0_TXD2/EHRPWM0_SYNCO/PRU1_R30[3]/PRU1_R31[3]/GPIO2[9]

LCDC

1547.88

单端50ohm

T1

T1/LCD_DATA4/GPMC_A4/PR1_MII0_TXD1/EQEP2A_IN/PRU1_R30[4]/PRU1_R31[4]/GPIO2[10]

LCDC

1579.25

单端50ohm

T2

T2/LCD_DATA5/GPMC_A5/PR1_MII0_TXD0/EQEP2B_IN/PRU1_R30[5]/PRU1_R31[5]/GPIO2[11]

LCDC

1581.7

单端50ohm

T3

T3/LCD_DATA6/GPMC_A6/PR1_EDIO_DATA_IN6/EQEP2_INDEX/PR1_EDIO_DATA_OUT6/PRU1_R30[6]/PRU1_R31[6]/GPIO2[12]

LCDC

1508.41

单端50ohm

T4

T4/LCD_DATA7/GPMC_A7/PR1_EDIO_DATA_IN7/EQEP2_STROBE/PR1_EDIO_DATA_OUT7/PRU1_R30[7]/PRU1_R31[7]/GPIO2[13]

LCDC

1578.66

单端50ohm

U1

U1/LCD_DATA8/GPMC_A12/EHRPWM1_TRIPZONE_INPUT/MCASP0_ACLKX/UART5_TXD/PR1_MII0_RXD3/UART2_CTSN/GPIO2[14]

LCDC

1622.21

单端50ohm

U2

U2/LCD_DATA9/GPMC_A13/EHRPWM0_SYNCO/MCASP0_FSX/UART5_RXD/PR1_MII0_RXD2/UART2_RTSN/GPIO2[15]

LCDC

1627.16

单端50ohm

U3

U3/LCD_DATA10/GPMC_A14/EHRPWM1A/MCASP0_AXR0/PR1_MII0_RXD1/UART3_CTSN/GPIO2[16]

LCDC

1700.94

单端50ohm

U4

U4/LCD_DATA11/GPMC_A15/EHRPWM1B/MCASP0_AHCLKR/MCASP0_AXR2/PR1_MII0_RXD0/UART3_RTSN/GPIO2[17]

LCDC

1708.13

单端50ohm

V2

V2/LCD_DATA12/GPMC_A16/EQEP1A_IN/MCASP0_ACLKR/MCASP0_AXR2/PR1_MII0_RXLINK/UART4_CTSN/GPIO0[8]

LCDC

1671.5

单端50ohm

V3

V3/LCD_DATA13/GPMC_A17/EQEP1B_IN/MCASP0_FSR/MCASP0_AXR3/PR1_MII0_RXER/UART4_RTSN/GPIO0[9]

LCDC

1644.43

单端50ohm

V4

V4/LCD_DATA14/GPMC_A18/EQEP1_INDEX/MCASP0_AXR1/UART5_RXD/PR1_MII_MR0_CLK/UART5_CTSN/GPIO0[10]

LCDC

1631.37

单端50ohm

T5

T5/LCD_DATA15/GPMC_A19/EQEP1_STROBE/MCASP0_AHCLKX/MCASP0_AXR3/PR1_MII0_RXDV/UART5_RTSN/GPIO0[11]

LCDC

1753.93

单端50ohm

U5

U5/LCD_VSYNC/GPMC_A8/GPMC_A1/PR1_EDIO_DATA_IN2/PR1_EDIO_DATA_OUT2/PRU1_R30[8]/PRU1_R31[8]/GPIO2[22]

LCDC

1529.28

单端50ohm

R5

R5/LCD_HSYNC/GPMC_A9/GPMC_A2/PR1_EDIO_DATA_IN3/PR1_EDIO_DATA_OUT3/PRU1_R30[9]/PRU1_R31[9]/GPIO2[23]

LCDC

1541.34

单端50ohm

V5

V5/LCD_PCLK/GPMC_A10/PR1_MII0_CRS/PR1_EDIO_DATA_IN4/PR1_EDIO_DATA_OUT4/PRU1_R30[10]/PRU1_R31[10]/GPIO2[24]

LCDC

1577.22

单端50ohm

R6

R6/LCD_AC_BIAS_EN/GPMC_A11/PR1_MII1_CRS/PR1_EDIO_DATA_IN5/PR1_EDIO_DATA_OUT5/PRU1_R30[11]/PRU1_R31[11]/GPIO2[25]

LCDC

1556.63

单端50ohm

U10

U10/GPMC_AD8/LCD_DATA23/MMC1_DAT0/MMC2_DAT4/EHRPWM2A/PR1_MII_MT0_CLK/GPIO0[22]

LCDC

1283.82

单端50ohm

T10

T10/GPMC_AD9/LCD_DATA22/MMC1_DAT1/MMC2_DAT5/EHRPWM2B/PR1_MII0_COL/GPIO0[23]

LCDC

1333.78

单端50ohm

T11

T11/GPMC_AD10/LCD_DATA21/MMC1_DAT2/MMC2_DAT6/EHRPWM2_TRIPZONE_INPUT/PR1_MII0_TXEN/GPIO0[26]

LCDC

1301.94

单端50ohm

U12

U12/GPMC_AD11/LCD_DATA20/MMC1_DAT3/MMC2_DAT7/EHRPWM0_SYNCO/PR1_MII0_TXD3/GPIO0[27]

LCDC

1314.77

单端50ohm

T12

T12/GPMC_AD12/LCD_DATA19/MMC1_DAT4/MMC2_DAT0/EQEP2A_IN/PR1_MII0_TXD2/PRU0_R30[14]/GPIO1[12]

LCDC

1397.62

单端50ohm

R12

R12/GPMC_AD13/LCD_DATA18/MMC1_DAT5/MMC2_DAT1/EQEP2B_IN/PR1_MII0_TXD1/PRU0_R30[15]/GPIO1[13]

LCDC

1437.4

单端50ohm

V13

V13/GPMC_AD14/LCD_DATA17/MMC1_DAT6/MMC2_DAT2/EQEP2_INDEX/PR1_MII0_TXD0/PRU0_R31[14]/GPIO1[14]

LCDC

1319.87

单端50ohm

U13

U13/GPMC_AD15/LCD_DATA16/MMC1_DAT7/MMC2_DAT3/EQEP2_STROBE/PR1_ECAP0_PWM/PRU0_R31[15]/GPIO1[15]

LCDC

1405.81

单端50ohm

T9

T9/GPMC_AD7/MMC1_DAT7/GPIO1[7]

GPMC

2829.76

单端50ohm

R9

R9/GPMC_AD6/MMC1_DAT6/GPIO1[6]

GPMC

2868.19

单端50ohm

V8

V8/GPMC_AD5/MMC1_DAT5/GPIO1[5]

GPMC

2864.81

单端50ohm

U8

U8/GPMC_AD4/MMC1_DAT4/GPIO1[4]

GPMC

2917.48

单端50ohm

T8

T8/GPMC_AD3/MMC1_DAT3/GPIO1[3]

GPMC

2760.02

单端50ohm

R8

R8/GPMC_AD2/MMC1_DAT2/GPIO1[2]

GPMC

2777.15

单端50ohm

V7

V7/GPMC_AD1/MMC1_DAT1/GPIO1[1]

GPMC

2779.79

单端50ohm

U7

U7/GPMC_AD0/MMC1_DAT0/GPIO1[0]

GPMC

2752.93

单端50ohm

U9

U9/GPMC_CSN1/MMC1_CLK/GPIO1[30]

GPMC

2551.92

单端50ohm

V9

V9/GPMC_CSN2/MMC1_CMD/GPIO1[31]

GPMC

2403.56

单端50ohm

T13

T13/GPMC_CSN3/GPMC_A3/RMII2_CRS_DV/MMC2_CMD/PR1_MII0_CRS/PR1_MDIO_DATA/EMU4/GPIO2[0]

GPMC

1882.5

单端50ohm

T7

T7/GPMC_OEN_REN/TIMER7/GPIO2[3]

GPMC

2717.59

单端50ohm

U6

U6/GPMC_WEN/TIMER6/GPIO2[4]

GPMC

2611.5

单端50ohm

R7

R7/GPMC_ADVN_ALE/TIMER4/GPIO2[2]

GPMC

2621.95

单端50ohm

T6

T6/GPMC_BE0N_CLE/TIMER5/GPIO2[5]

GPMC

2549.22

单端50ohm

U18

U18/GPMC_BE1N/GMII2_COL/GPMC_CSN6/MMC2_DAT3/GPMC_DIR/PR1_MII1_RXLINK/MCASP0_ACLKR/GPIO1[28]

GPMC

1542.96

单端50ohm

T17

T17/GPMC_WAIT0/GMII2_CRS/GPMC_CSN4/RMII2_CRS_DV/MMC1_SDCD/PR1_MII1_COL/UART4_RXD/GPIO0[30]

GPMC

2561.9

单端50ohm

U17

U17/GPMC_WPN/GMII2_RXER/GPMC_CSN5/RMII2_RXER/MMC2_SDCD/PR1_MII1_TXEN/UART4_TXD/GPIO0[31]

GPMC

1192.7

单端50ohm

V12

V12/GPMC_CLK/LCD_MEMORY_CLK/GPMC_WAIT1/MMC2_CLK/PR1_MII1_CRS/PR1_MDIO_MDCLK/MCASP0_FSR/GPIO2[1]

GPIO

1344.21

单端50ohm

R13

R13/GPMC_A0/GMII2_TXEN/RGMII2_TCTL/RMII2_TXEN/GPMC_A16/PR1_MII_MT1_CLK/EHRPWM1_TRIPZONE_INPUT/GPIO1[16]

RGMII2

1420.07

单端50ohm

V14

V14/GPMC_A1/GMII2_RXDV/RGMII2_RCTL/MMC2_DAT0/GPMC_A17/PR1_MII1_TXD3/EHRPWM0_SYNCO/GPIO1[17]

RGMII2

1309.08

单端50ohm

U14

U14/GPMC_A2/GMII2_TXD3/RGMII2_TD3/MMC2_DAT1/GPMC_A18/PR1_MII1_TXD2/EHRPWM1A/GPIO1[18]

RGMII2

1278.94

单端50ohm

T14

T14/GPMC_A3/GMII2_TXD2/RGMII2_TD2/MMC2_DAT2/GPMC_A19/PR1_MII1_TXD1/EHRPWM1B/GPIO1[19]

RGMII2

1278.38

单端50ohm

R14

R14/GPMC_A4/GMII2_TXD1/RGMII2_TD1/RMII2_TXD1/GPMC_A20/PR1_MII1_TXD0/EQEP1A_IN/GPIO1[20]

RGMII2

1303.28

单端50ohm

V15

V15/GPMC_A5/GMII2_TXD0/RGMII2_TD0/RMII2_TXD0/GPMC_A21/PR1_MII1_RXD3/EQEP1B_IN/GPIO1[21]

RGMII2

1177.36

单端50ohm

U15

U15/GPMC_A6/GMII2_TXCLK/RGMII2_TCLK/MMC2_DAT4/GPMC_A22/PR1_MII1_RXD2/EQEP1_INDEX/GPIO1[22]

RGMII2

1207.75

单端50ohm

T15

T15/GPMC_A7/GMII2_RXCLK/RGMII2_RCLK/MMC2_DAT5/GPMC_A23/PR1_MII1_RXD1/EQEP1_STROBE/GPIO1[23]

RGMII2

1245.03

单端50ohm

V16

V16/GPMC_A8/GMII2_RXD3/RGMII2_RD3/MMC2_DAT6/GPMC_A24/PR1_MII1_RXD0/MCASP0_ACLKX/GPIO1[24]

RGMII2

1155.2

单端50ohm

U16

U16/GPMC_A9/GMII2_RXD2/RGMII2_RD2/MMC2_DAT7/GPMC_A25/PR1_MII_MR1_CLK/MCASP0_FSX/GPIO1[25]

RGMII2

1184.34

单端50ohm

T16

T16/GPMC_A10/GMII2_RXD1/RGMII2_RD1/RMII2_RXD1/GPMC_A26/PR1_MII1_RXDV/MCASP0_AXR0/GPIO1[26]

RGMII2

1382.51

单端50ohm

V17

V17/GPMC_A11/GMII2_RXD0/RGMII2_RD0/RMII2_RXD0/GPMC_A27/PR1_MII1_RXER/MCASP0_AXR1/GPIO1[27]

RGMII2

1275.61

单端50ohm

M16

M16/GMII1_RXD0/RMII1_RXD0/RGMII1_RD0/MCASP1_AHCLKX/MCASP1_AHCLKR/MCASP1_ACLKR/MCASP0_AXR3/GPIO2[21]

RGMII1

820.98

单端50ohm

L15

L15/GMII1_RXD1/RMII1_RXD1/RGMII1_RD1/MCASP1_AXR3/MCASP1_FSR/EQEP0_STROBE/MMC2_CLK/GPIO2[20]

RGMII1

814.61

单端50ohm

L16

L16/GMII1_RXD2/UART3_TXD/RGMII1_RD2/MMC0_DAT4/MMC1_DAT3/UART1_RIN/MCASP0_AXR1/GPIO2[19]

RGMII1

814.85

单端50ohm

L17

L17/GMII1_RXD3/UART3_RXD/RGMII1_RD3/MMC0_DAT5/MMC1_DAT2/UART1_DTRN/MCASP0_AXR0/GPIO2[18]

RGMII1

813.68

单端50ohm

L18

L18/GMII1_RXCLK/UART2_TXD/RGMII1_RCLK/MMC0_DAT6/MMC1_DAT1/UART1_DSRN/MCASP0_FSX/GPIO3[10]

RGMII1

835.86

单端50ohm

J17

J17/GMII1_RXDV/LCD_MEMORY_CLK/RGMII1_RCTL/UART5_TXD/MCASP1_ACLKX/MMC2_DAT0/MCASP0_ACLKR/GPIO3[4]

RGMII1

845.81

单端50ohm

K17

K17/GMII1_TXD0/RMII1_TXD0/RGMII1_TD0/MCASP1_AXR2/MCASP1_ACLKR/EQEP0B_IN/MMC1_CLK/GPIO0[28]

RGMII1

688.77

单端50ohm

K16

K16/GMII1_TXD1/RMII1_TXD1/RGMII1_TD1/MCASP1_FSR/MCASP1_AXR1/EQEP0A_IN/MMC1_CMD/GPIO0[21]

RGMII1

674.67

单端50ohm

K15

K15/GMII1_TXD2/DCAN0_RX/RGMII1_TD2/UART4_TXD/MCASP1_AXR0/MMC2_DAT2/MCASP0_AHCLKX/GPIO0[17]

RGMII1

688.83

单端50ohm

J18

J18/GMII1_TXD3/DCAN0_TX/RGMII1_TD3/UART4_RXD/MCASP1_FSX/MMC2_DAT1/MCASP0_FSR/GPIO0[16]

RGMII1

667

单端50ohm

K18

K18/GMII1_TXCLK/UART2_RXD/RGMII1_TCLK/MMC0_DAT7/MMC1_DAT0/UART1_DCDN/MCASP0_ACLKX/GPIO3[9]

RGMII1

665.33

单端50ohm

J16

J16/GMII1_TXEN/RMII1_TXEN/RGMII1_TCTL/TIMER4/MCASP1_AXR0/EQEP0_INDEX/MMC2_CMD/GPIO3[3]

RGMII1

689.08

单端50ohm

M17

M17/MDIO_DATA/TIMER6/UART5_RXD/UART3_CTSN/MMC0_SDCD/MMC1_CMD/MMC2_CMD/GPIO0[0]

MDIO

840.44

单端50ohm

M18

M18/MDIO_CLK/TIMER5/UART5_TXD/UART3_RTSN/MMC0_SDWP/MMC1_CLK/MMC2_CLK/GPIO0[1]

MDIO

776.47

单端50ohm

F17

F17/MMC0_DAT3/GPMC_A20/UART4_CTSN/TIMER5/UART1_DCDN/PRU0_R30[8]/PRU0_R31[8]/GPIO2[26]

MMC0

622.16

单端50ohm

F18

F18/MMC0_DAT2/GPMC_A21/UART4_RTSN/TIMER6/UART1_DSRN/PRU0_R30[9]/PRU0_R31[9]/GPIO2[27]

MMC0

626.02

单端50ohm

G15

G15/MMC0_DAT1/GPMC_A22/UART5_CTSN/UART3_RXD/UART1_DTRN/PRU0_R30[10]/PRU0_R31[10]/GPIO2[28]

MMC0

715.46

单端50ohm

G16

G16/MMC0_DAT0/GPMC_A23/UART5_RTSN/UART3_TXD/UART1_RIN/PRU0_R30[11]/PRU0_R31[11]/GPIO2[29]

MMC0

659.75

单端50ohm

G17

G17/MMC0_CLK/GPMC_A24/UART3_CTSN/UART2_RXD/DCAN1_TX/PRU0_R30[12]/PRU0_R31[12]/GPIO2[30]

MMC0

669.17

单端50ohm

G18

G18/MMC0_CMD/GPMC_A25/UART3_RTSN/UART2_TXD/DCAN1_RX/PRU0_R30[13]/PRU0_R31[13]/GPIO2[31]

MMC0

627.97

单端50ohm

N17

N17/USB0_DP

USB0

1070.04

差分90ohm

N18

N18/USB0_DM

USB0

1066.26

差分90ohm

R17

R17/USB1_DP

USB1

1155.92

差分90ohm

R18

R18/USB1_DM

USB1

1154.08

差分90ohm

5.3 其他设计注意事项

保留Micro SD 卡接口

评估底板通过MMC0总线引出Micro SD卡接口,主要用于调试过程中使用Linux系统启动卡来启动系统,或批量生产时可基于Micro SD卡快速固化系统,底板设计时建议保留此外设接口。

保留UART3接口

评估底板将UART3_RXD(C15)和UART3_TXD(C18)引脚通过CH340T芯片引到Micro USB接口,作为系统调试串口使用,底板设计时建议保留UART3作为系统调试串口。

图 19

保留JTAG接口

评估底板引出14pin JTAG接口,为便于系统的调试,底板设计时建议保留此接口。

相关问答

储存器的接口是啥意思?外部存储器接口外部存储器接口(ExternalMemoryInterface,简称EMIF)是TMSDSP器件上的一种接口,具体可以分为EMIFA和EMIFB。一般来说,EMIF可实现DSP与...