铠侠正在研发七级单元的3D NAND闪存,主控芯片开发亦成为难点

NAND闪存制造商一直尝试增加每个单元存储的位数来提高存储密度,从成本角度出发,这是一种非常具有价值的方法。Kioxia(铠侠)在这方面一直非常积极,早在2019年就开始讨论五级单元的PLC 3D NAND闪存,去年还曾展示六级单元的HLC 3D NAND闪存。

据PC Watch报道,铠侠表示目前正在开发七级单元的3D NAND闪存,暂时只能在实验室的低温条件下实现,并在今年的IMW 2022会议上介绍了相关的研究成果。目前七级单元的3D NAND闪存还没有正式的名字,反倒是去年展望3D NAND闪存发展的时候,确定八级单元的名字叫OLC。目前铠侠将芯片浸入在液氮(温度77K / 零下196摄氏度)环境中,让使用的材料变得更加稳定,同时可以降低电压的要求。

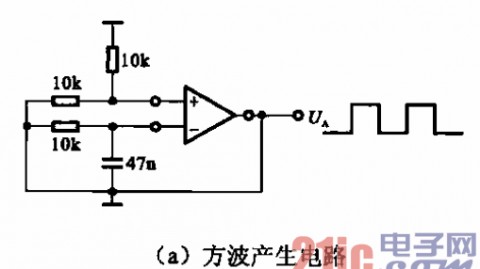

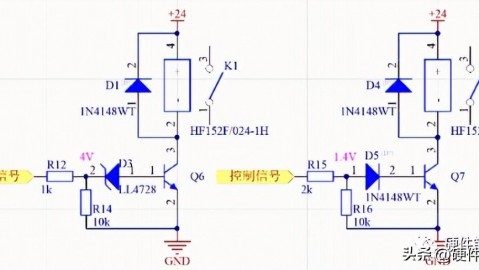

找到合适的材料和结构只是挑战超高密度NAND闪存的一部分,研究人员还要开发必要的主控芯片,以控制128级的电压变化。目前市场上常见的四级单元的QLC 3D NAND闪存,电压变化也就16级,显然七级单元的3D NAND闪存的难度要大得多。自2000年二级单元的MLC 3D NAND闪存出现以来,主控芯片变得越来越复杂,开发和制造成本也越来越高。即便闪存芯片的价格下降了,主控芯片的价格上涨也会抹掉成本优势。

铠侠的合作伙伴西部数据认为,从QLC过渡到PLC的过程会比较慢,至少到2025年以后,市场上才会出现搭载PLC 3D NAND闪存的产品,显然六/七级单元的3D NAND闪存距离消费者更加遥远。

英特尔先进工艺再次难产,芯片制造为什么难住了一众英雄好汉?

芯片制造的难,就是难在不断地向物理极限发起挑战,而且你不知道这个物理极限到底在哪里。

不同种类的芯片所面临的物理极限的挑战是不一样的,我们来分类看一下。

先来看3D-NAND芯片

NAND这个词在外行的看来比较陌生,但实际上离我们并不遥远,我们买的很多固态硬盘的核心存储芯片,就是3D-NAND芯片。

3D NAND芯片的内部结构就像一座住宅大厦,里面有很多的“小房子”(下图中的memory cell),它们就是电荷存储的物理空间。

3D NAND芯片结构示意图,图片来源:semiengineering.com

为什么叫做3D NAND,因为原来的NAND的“小房子”只能盖一层,是平面型的,故而称作2D NAND,而3D NAND可以在垂直方向上叠加“小房子”,是一个立体的结构。

这些“小房子”是基于半导体制造几大基本模块工艺批量制作的。每一个"小房子"的组成,是经过精确设计的导体/半导体/绝缘材料。

3D NAND memory cell 示意图,来源:西部数据

国产3D NAND芯片之所以落后,就是在于国产芯片的堆叠层数较低,目前国产芯片量产最高可以做到64层(长江存储128层QLC 3D NAND 闪存目前仅通过测试,尚未量产),而一线大厂,如三星、海力士、镁光等,已经可以做到128层及以上。

叠加的层数越多,工艺制造上遭遇的难度与问题就会越大,电路搭错的几率就会越高。

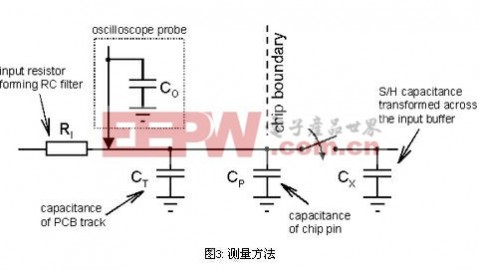

3D NAND芯片的制造难度在于:在水平方向上,要解决增加图案密度的问题,以增加存储密度;在垂直方向上,又要解决高深宽比(HAR)刻蚀均匀性的问题。

下图展示的就是一道高深宽比刻蚀的缺陷,正常的情况下,dry etch工艺都会呈现出垂直或者梯形的形貌,而随着深宽比的加大,竟然还观察到了中间刻蚀出“胖肚子”的形貌。

图片来源:Y. Ye, Z. Xia, L. Liu and Z. Huo, 2018 14th IEEE ICSICT 2018, pp. 1-3

这是长江存储与一些科研机构在联合研发过程中遭遇到的一个真实案例。

实际上,在芯片研发与制造过程中,类似的例子数不胜数,新的工艺失效模型永远在颠覆着我们的认知,有的时候甚至会感叹这是一门玄学,我们要做的,就是不断地挑战微观控制的极限。

再来说一下逻辑芯片

我们日常接触的CPU芯片、显卡芯片都隶属于此范畴。

逻辑芯片在器件上要解决的首要问题就是,随着随着摩尔定律的推进以及尺寸的缩小,CMOS器件在某些电性能方面出现了衰退,这就需要新的器件设计。

但逻辑芯片不仅仅要解决微电子器件的问题,当尺寸缩小之后,工艺难度也会进一步加大。

比如,为了让尺寸缩小,分辨率更高,光刻工艺会采用浸没式光刻。所谓的浸没式,就是让光源与光刻胶之间使用水来充当光路介质,这就对光刻机台以及工艺提出更高的挑战。

尺寸的缩小不仅仅体现在图案的尺寸上,垂直方向上的薄膜高度的要求也越来越高。在这样的背景下,原子层沉积(ALD)技术被发明出来,这样在薄膜厚度上可以精确地控制到只有几层原子的厚度。

但是,工艺越先进,工艺缺陷与失败的几率也会增加,其原因,用业界术语来说,就是工艺的window在缩小。所谓的window,就是允许的工艺参数浮动的范围。在关键的步骤里,一旦工艺指标跑出了限定标准,芯片制造失败的风险就会大大增加。因此,越是先进的工艺,就越要保证工艺的稳定性。

而且,也会出现很多很“玄学”的现象。

比如,在先进节点的dry etch工艺中,往往会出现”pitch walking“现象。

Pitch walking,是指芯片某一层图案的周期结构并没有按照掩膜版的设计呈现,而是出现了个别线条的挪动,它会导致图案的周期性受到破坏。

上述的例子还仅仅是涉及单一模块工艺,更繁琐的是工艺集成。

芯片的制造上是一个成百上千步的过程,前后步之间相互影响非常大。

这里我做一个比喻,方便大家理解。

假如我要挖一口井,原来的时候,我按照标准工艺去挖井就好了,现在有人说,井下的石头层是一种罕见的类型,特别容易渗水,那挖井的工艺就要做相应的调整。

很多时候,前步出现了工艺调整,后步就要相应地做出调整,而调整多少,怎么调整,带来的是正面影响还是负面影响,往往都是未知的。这就需要不断地进行工艺验证以及新工艺的开发。这就会让芯片研发的周期延长。

而消费者那边,还在苦苦盼望着更先进芯片的上市。殊不知,芯片厂里面数百数千的研发工程师,用尽了他们学到的所有科学知识,消耗了本已残存不多的脑细胞,甚至是放弃了美好的个人时间,辛苦搬砖,他们远比消费者还想让芯片尽快面市。

参考文献:

Y. Ye, Z. Xia, L. Liu and Z. Huo, 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT) 2018, pp. 1-3.Y. M. Yang, S. W. Lim, J. Hong, M. Park, Y. Yang, W. K. Cho, C. Adams, M. Aminpur and C. H. Maeng, 2018 IEEE International Interconnect Technology Conference (IITC) 2018, pp. 79-81.相关问答

芯片 的研发尺寸到一纳米之后怎么办,是不是要另寻出路?1nm工艺制程并不是芯片的极限今年3月份台积电与台湾国立交通大学的研究团队因为成功开发出了大面积晶圆尺寸的单层氮化硼(BN)而登上了《自然》杂志,厚度仅0.7...

50纳米 芯片 实现量产意味着什么?近日,恒烁半导体推出了一款面向物联网应用的50nm/128Mb高速低功耗NORFlash存储芯片,具有很强的成本和性能优势,力争在该市场中站稳脚跟,迎接IoT时代的真正爆...

5nm刻蚀机厂家有几家?作为全球最大的芯片消费市场,截至2019年中国芯片市场规模已经增长到3104亿美元,与10年前相比扩大了140%。而近些年来,中国开始意识到芯片自给的重要性,因此芯...

国产 芯片 发展到什么水平了?芯片制造的差距并不是单个方面,它是工艺的各个方面。许多智能手机或电脑都是中国制造,但是装有的中国“芯”却寥寥无几。以前国家对微电子的重视程度是不够的...

合肥长鑫和长江存储两个企业的存储 芯片 和未来发展哪个更有潜力?合肥长鑫和长江存储两个企业的存储芯片和未来发展哪个更有潜力?闪存也好内存也罢都是国内相当薄弱的环节,都是要在国外垄断企业口里夺食,如果发展得好都是相当...

如何根据u盘固件相关主控参数对译码表修复u盘,提取数据 - 珍...很多人都有疑问,U盘坏了还能进行数据恢复吗?一、U盘为什么会无法识别?将U盘拆解后,可以发现,U盘中只有两类主要芯片,NAND控制芯片和NAND存储芯片,其...

如何根据u盘固件相关主控参数对译码表修复u盘,提取数据 - ah...flash闪存内的数据一般不会丢失,如果仅是主控板部分故障,简单的维修好主控部分就可以解决,或者干脆换同型号的主控板,数据即可恢复。如果是闪存芯片...

如何看待紫光DDR4内存开始量产?但值得一提的是,兆易创新对此定下的目标是,该工艺的良率在10%以上。上面说了DRAM内存,顺便再说一下NAND闪存。紫光除了要生产DRAM内存外,还在研发NAND闪存芯...

Android系统执行机制和碎片改变不了吗?为什么呢?首先,我们需要知道为什么Android之前很容易卡顿。关于这个答案,一直以来都是众说纷纭,有人说Android卡是因为系统资源分配不均,有人说是因为用的越久垃圾文件...

内存价格什么时候可以回落?国产内存的前景如何?长期以来,我国半导体行业发展落后,没有量产芯片颗粒的能力,严重依赖国外芯片颗粒。在中国的进口贸易中,仅2016年1月份到10月份,中国在进口芯片上就花费...20...