闪存颗粒到底是何物?浅析闪存及制程

如果用一个词来描述2016年的固态硬盘市场的话,那么闪存颗粒绝对是会被提及的一个关键热词。在过去的2016年里,围绕着闪存颗粒发生了一系列大事,包括闪存颗粒的量产引发固态涨价,闪存颗粒的制程问题引发的厂商竞争,以及“日经贴”般的MLC/TLC颗粒的优劣问题。

那么,到底什么是闪存颗?2D NAND和3D NAND之间又有哪些区别和联系?下面,我们一一来解读。

闪存颗粒到底是什么?

闪存颗粒,又称闪存,是一种非易失性存储器,即在断电的情况下依旧可以保存已经写入的数据,而且是以固定的区块为单位,而不是以单个的字节为单位。

根据用途和规格不同,闪存颗粒有很多不同的变种,今天我们主要讨论的是用于固态硬盘等存储设备中的、最为常用的NAND闪存颗粒。

NAND闪存颗粒,是闪存家族的一员,最早由日立公司于1989年研制并推向市场,由于NAND闪存颗粒有着功耗更低、价格更低和性能更佳等诸多优点,成为了存储行业最为重要的存储原料。

根据NAND闪存中电子单元密度的差异,又可以分为SLC(单层次存储单元)、MLC(双层存储单元)以及TLC(三层存储单元),此三种存储单元在寿命以及造价上有着明显的区别。

在这里我们就不再展开讨论了。

2D和3D闪存之间的区别和联系

在解释3D NAND之前,我们先得弄清楚2D NAND是什么,以及“2D”和“3D”的真实含义。

首先是2D NAND,我们知道在数学和物理领域,2D/3D都是指的方向,都是指的坐标轴,“2D”指的是平面上的长和宽,而“3D”则是在“2D”基础上,添加了一个垂直方向的“高”的概念。

由此,2D NAND真实的含义其实就是一种颗粒在单die内部的排列方式,是按照传统二维平面模式进行排列闪存颗粒的。

相对应的,3D NAND则是在二维平面基础上,在垂直方向也进行颗粒的排列,即将原本平面的堆叠方式,进行了创新。

利用新的技术(即3D NAND技术)使得颗粒能够进行立体式的堆叠,从而解决了由于晶圆物理极限而无法进一步扩大单die可用容量的限制,在同样体积大小的情况下,极大的提升了闪存颗粒单die的容量体积,进一步推动了存储颗粒总体容量的飙升。

同时,在业界,根据在垂直方向堆叠的颗粒层数不同,和选用的颗粒种类不同,3D NAND颗粒又可以分为32层、48层甚至64层 3D TLC/MLC颗粒的不同产品,这取决于各大原厂厂商的技术储备和实际选用的颗粒种类。

我们可以打个比方,来理解2D NAND和3D NAND技艺之间的区别和联系。

2D NAND就如同在一块有限的平面上建立的数间平房,这些平房整齐排列,但是随着需求量的不断增加,平房的数量不断井喷,可最终这块面积有限的平面只能容纳一定数量的平房而无法继续增加;

3D NAND则就如同在同一块平面上盖起的楼房,在同样的平面中,楼房的容积率却远远高于平房,因而它能提供更多的空间,也就是提供了更大的存储空间,而32层、48层以及64层,则就是这些楼房的高度,一共堆叠了多少层。

虽然,3D NAND技术能够在同等体积下,提供更多的存储空间,但是这项堆叠技术对于原厂制造商来说有着相当的操作难度,需要原厂有着相当的技术积累,因而目前能够掌握3D NAND技术的原厂公司十分少见,只有三星、美光等少数公司的3D NAND颗粒实现了量产和问世。

你真的懂3D NAND闪存?|半导体行业观察

来源:内容由 微信公众号 半导体行业观察 (ID:icbank) 综合自「非凡创芯力」,谢谢。

从新闻到市场分析报告,我们看到很多关于 3D NAND 的报道,国内这几年投资兴建许多12吋半导体工厂,其中大多是晶圆代工或 DRAM 厂,排除外资所投资的半导体厂,长江存储 (YMTC) 的武汉新芯 (XMC) 是目前唯一即将量产 3D NAND 的国内厂家。武汉新芯已研发出 32 层 3D NAND 芯片,预计年底量产,不过据消息指出,截至九月底武汉新芯已有约 2,000 片产能。

本篇文章将带大家初步了解 3D NAND 是什么、为何发展 3D NAND 技术、3D NAND 有哪些技术发展,以及,它所带来的影响。

NOR Flash及NAND Flash

在开始之前,我们先来科普一下ㄧ些 Flash Memory 的基本知识。在半导体存储器领域,NAND 是 NAND Flash Memory 的简称,Flash Memory 在国内翻译为快闪存储器,简称闪存,是ㄧ种非易失性存储器 (Non-Volatile Memory,NVM),也就是说当电源关掉,它所存储的数据不会消失。与之对应,大家常听到的 DRAM、SRAM 则是易失性存储器 (Volatile Memory, VM),电源关掉,所存储的数据会消失。

闪存依存储单元 (Memory Cell) 结构的不同区分为 NOR Flash及 NAND Flash 二种,对于这二种闪存的差异,技术细节我们不在此细说,读者只需知道:(请参考下表)

NOR Flash: 有较快的读取速度,但写入及擦除则较慢,其容量也远小于 NAND Flash,但 NOR Flash 可存取至任何选定的字节。ㄧ般 IC 内之嵌入式闪存 (Embedded Flash) 均为 NOR Flash,主要用于存储行动装置及计算机内之启动、应用程序、操作系统和就地执行 (eXecute-in-Place,XIP) 的代码。NOR Flash 存储单元大小比 NAND Flash大很多,也由于存储单元的结构,NOR Flash 在本质上比 NAND Flash可靠。

NAND Flash: 读取速度稍慢,但写入及擦除则相对较 NOR Flash 快很多,IC 容量可达 128GB 以上,但它无法存取至特定的字节,而是以小块 (Page) 方式处理数据。NAND Flash 通常被用来作为大量数据存储器,现在市面上 GB (Gigabyte) 级的 U 盘 (USB Flash Drive) 及 SSD 固态硬盘 (Solid State Drive/Disk) 均使用 NAND Flash。

图片来源 : Created by Author

闪存缩放限制

(Flash Memory Scaling Limit)

小存储单元尺寸 (Cell Size)、高性能 (Performance) 以及低功耗 (Power Consumption) 一直是存储器业者持续追求的目标。越来越小的尺寸让每片晶圆可以生产更多的 die,高性能才能符合高速运算的需求,低耗电才能改善行动装置电池充电频率及数据中心系统散热的问题。而芯片工艺的每一次提升 (24nm → 14nm → 10nm…) ,带来的不仅仅是元件尺寸的缩小,同时也带来性能的增强和功耗的降低。

有个词称为 ”闪存的缩放限制” (Flash Memory Scaling Limit),指出无论芯片上的元件能缩小多少,闪存都无法跟上步伐。这个限制过去十多年ㄧ直都没实现,然而,14nm 以下,半导体工艺迁移到 Fin-FET (Fin Field-Effect Transistor,鳍式场效应晶体管) 结构,一种新的晶体管,让这个 ”闪存缩放限制” 问题正式浮出水面,因为这技术无法直接套用在既有的闪存元件上。嵌入式 NOR Flash 在这方面目前似乎无解,幸好过去几年,ㄧ些新的存储器元件技术已被开发出来,嵌入式 NOR Flash 被取代应该只是时间早晚的问题,相反的,NAND Flash 业者却早已找到ㄧ些因应之道。

为了打破 ”闪存的缩放限制” 枷锁,确保能持续提供高容量、低成本的 NAND Flash,相关业者多年前就开始研发解决之道。主要的方向有:

3D NAND Flash : 把存储单元立体化

多层单元 (Multi-Level Cell) : 让每个存储单元不只存储ㄧ个 bit

硅穿孔技术 (TSV,Through Silicon Via) : 让多颗闪存晶粒可以直接堆叠封装

很多文章将第ㄧ项及第三项混淆在ㄧ起,下面我们将ㄧㄧ介绍,协助大家了解。

3D NAND Flash

那到底什么是 3D NAND ? 它指的是 NAND 闪存的存储单元是 3D 的。我们之前使用的闪存多属于平面闪存 (Planar NAND),而 3D NAND,顾名思义,就是它是立体的。Intel 用高楼大厦为例演释 3D NAND,如果平面闪存是平房,那 3D NAND 就是高楼大厦。把存储单元立体化,这意味着每个存储单元的单位面积可以大幅下降。下图为 Samsung Planar NAND 发展至 3D NAND (V-NAND) 的示意图。

图片来源 : Samsung V-NAND technology White Paper (Modi

左边二个是 Planar NAND,只是存储单元结构不同,由浮动栅结构 (Floating Gate) 迁移至电荷撷取闪存,亦即上图之 2D CTF (Charge Trap Flash)。然后是将 2D CTF 存储单元 3D 化变成 3D CTF 存储单元 (上图之 3D CTF),最后通过工艺技术提升逐渐往上增加存储单元的 Layer 数,把存储单元像盖大楼ㄧ样越做越多层。Samsung 的 3D V-NAND 存储单元的层次 (Layer) 由 2009 年的 2-layer 逐渐提升至 24-layer、64-layer,再到今年 (2018) 之 96-layer。

图片来源 : Samsung V-NAND technology White Paper (Modi

近几年来许多大厂纷纷投入 3D NAND 的研发,但目前只有 Samsung、Toshiba/SanDisk/WD、SK Hynix、Micron/Intel 四组公司能够量产。各家的 3D NAND 存储单元及技术都不相同,也几乎每家公司都已宣布开发出 96 层 3D NAND,但目前量产的大多为 64 到 72 层的 3D NAND。

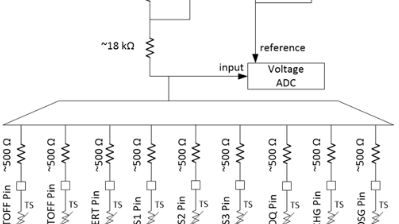

3D NAND 闪存工艺复杂,难度极高,因此厂商并非以最先进的工艺来研发生产 3D NAND。目前最先进的逻辑芯片工艺已来到 7nm,许多大厂目前量产的是 14nm,Planar NAND 也多使用 14nm 工艺生产,而 3D NAND 则大多使用 20nm 以上的工艺。下图是 Tech Insights 2018 最新整理的 NAND Flash Roadmap,包含 2D (Planar) NAND 及 3D NAND,注意到没,前面提到即将量产的长江存储 (武汉新芯) 已被纳入图表中,成为第五家有能力生产 3D NAND 的厂家。

图片来源 : Tech Insights NAND Flash Memory Technology/

多层单元

(Multi-Level Cell)

一般正常的存储单元,不管是 DRAM、SRAM、FLASH、ROM 等等,都只存储ㄧ个比特 (Bit) 的资料 (称为 SLC,Single-Level Cell)。为能更缩小存储单元尺寸,除了运用工艺持续做小及将存储单元 3D 化外,各厂商也将脑筋动到增加每存储单元能存储的 bit 数目上。简单的算数,当ㄧ个存储单元可以存储二个 bit 时 (称为 MLC,Multi-Level Cell),其存储单元尺寸等同于减少ㄧ半 ; 存储三个 bit (称为 TLC,Triple-Level Cell),则尺寸等同于原有的 1/3 ; 四个 bit (称为 QLC,Quad-Level Cell),则存储单元尺寸只剩原有的 1/4。(注: 也许当年在定义 2-Level Cell 时没想之后还会有 TLC 及 QLC,因此以 MLC 代表 2-Level Cell)。

SLC 存储ㄧ个 bit 数据,也就是二个状态 (0,1) ; MLC 存储二个 bit 数据,所以是四个状态 (00,01,10,11) ; TLC 三个 bit,八个状态 (000,001,010,011,100,101,110,111) ; QLC 四个 bit,十六个状态 (0000,0001,…. 1111),如下图所示。

图片来源 : Micron Official Website (Modified by Author

当然天下没有白吃的午餐,鱼与熊掌不可兼得,存储单元尺寸降低的代价是设计难度的提高以及性能的降低。为什么会如此?又是ㄧ个简单的算数问题。假设存储单元电压是 1.8V,对 SLC 而言,ㄧ个 bit 有二个状态,平均分配 1.8V 电压,每个状态可以分到 0.9V。对 MLC 而言,四个状态平均分配电压,每个状态可以分到 0.45V,以此类推,TLC 每个状态只可以分到 0.225V,而 QLC 更惨,每个状态只可以分到 0.1125V。在这么小的电压下,这么多的状态以极小的电压区隔,电压区隔越小越难控制,干扰也越复杂,而这些问题都会影响 TLC 或 QLC 闪存的性能、可靠性及稳定性,因而可以想见设计的难度有多高了。

另外如同上图所示,越往右,存储单元相对尺寸越小,因而成本越低。但其编程/擦除周期 (Program/Erase Cycle,简称 P/E Cycle,也有人称为擦写次数) 会大幅降低,同时读、写及擦除所需的时间也会增加 (性能降低)。擦写次数的降低为这项技术带来相当大的争议,因为擦写次数代表这闪存的寿命长短。如同上图所示,从 SLC 到 QLC,擦写次数由 10 万次降到只有ㄧ千次,吓坏ㄧ大堆人。

厂商当然也知道,他们用系统设计来弥补这项缺点。系统会控制平均分摊每一个区块的擦写次数,故障的区块也会被尚未使用的区块替换,以确保了闪存能持续运行。因为如此,即使每个存储单元只有ㄧ千次擦写次数,整颗闪存仍然可以从容的应付我们日常使用的需求。当然,这样的结果使得 TLC 或 QLC 只适用于消费者个人使用 (例如 SSD),它是无法满足 Data Center 之类的企业需求的,因为商用,例如资料处理中心 (Data Processing Center),的存储设备,其插写频率是相当相当高的。

硅穿孔技术

(TSV,Through Silicon Via)

硅穿孔技术其实与 3D NAND 工艺无关,严格来说,它属于ㄧ种封装技术。会拿出来讲主要是ㄧ方面它可让 3D NAND 闪存更上层楼,容量加大好几倍。另ㄧ个原因是因为有些人把它跟 3D NAND 存储单元的 layer 层数混淆了,他们把 32、64 或 96-layer 3D NAND 描述为把 32、64 或 96 个晶粒 (Die) 堆叠在ㄧ起,这是很大的误解。

TSV 技术已普遍用于 DRAM及 Flash 产品。以往ㄧ个 IC 芯片 (Chip) 只封装ㄧ颗晶粒,渐渐地为了降低成本、节省主机板空间及提高性能,多芯片封装 (MCP,Multi-Chip Package) 开始盛行 (如下图左方图示)。TSV 则是以工艺方式将 IC 基板 (Substrate) 穿孔,填入金属,让上下晶粒直接相导通 (如下图右方图示),不仅省去像左方图示所显示封装打线 (Bonding),更能进ㄧ步提升 DRAM 或 Flash 单颗芯片的容量、讯号品质、传输性能,以及降低传导杂讯干扰。

图片来源 : 3D NAND Flash Memory - Toshiba (Modified by

目前各家量产的 3D NAND 芯片大多只以 TSV 堆叠到 8 或 16 层 3D NAND 晶粒 (Die)。下表范例为 Toshiba 的 512GB (Gigabyte)/1TB (Terabyte) 闪存产品介绍,你可以清楚看到它使用 48-layer 的 3D NAND 存储工艺制造出容量为 512 Gb (Gigabit) 的闪存晶粒,再以 TSV 技术分别堆叠 8 或 16 个 die (在下表中是以 Number of Stacks 来表示堆叠数目) 来做出 512 GB (512Gb x 8) 或 1TB (512Gb x 16) 的闪存芯片。(注 : 小写的 b 代表 bit (比特),大写 B 代表 byte (字节),ㄧ个 byte 等于 8 个 bits)。

图片来源 : AnandTech Post : Toshiba Weds 3D NAND and T

所以,ㄧ个 NAND 闪存的晶粒 (die),运用 3D NAND 技术,可以把多达 96-layer 的存储单元堆叠在一起,像盖摩天大楼ㄧ样。而为了增加每个封装芯片 (Chip) 的容量,厂商再把8个或16个晶粒 (die) 以TSV 的技术叠在ㄧ起去封装成芯片。这样应该清楚了吧!

结语

半导体工艺来到 14nm 以下,Fin-FET 技术让 NAND 及 NOR 闪存的发展碰到瓶颈。半导体大厂运用三项技术,亦即 3D NAND 存储单元技术、多层单元 (MLC/TLC/QLC) 技术,以及,硅穿孔 (TSV) 技术,让 NAND 闪存得以持续发展,许多大厂都已开发出 96 层 TLC 甚至是 QLC 的 3D NAND 闪存。

NAND 闪存芯片的容量在这几年快速提升,因而使得 NAND 闪存芯片成为行动装置及计算机内之大量数据存储器芯片。SSD 固态硬盘的容量已可做到 1TB (Terabyte) 等级,逼近 HDD 传统硬盘 (Hard Disk Drive)。虽然在未来几年 HDD 仍然有些许价格上的优势 (SSD 每 GB 的单价约为 $0.2~$0.3,是 HDD 的10 倍),但由于 SSD 不像 HDD 有机械动作,速度、噪音及耗电也都比 HDD 好,已普遍受到ㄧ般消费者的欢迎,然而由于低擦写次数等限制,使得 3D NAND SSD 无法取代 HDD 在商用市场上的地位。

许多新型态的非易失性存储器已研发出来 (我们将另文介绍),未来或许能取代现有的 DRAM/SRAM/Flash 存储器。在此之前,3D NAND 闪存应该仍可保有它的市场地位ㄧ段时间。

最后,附带ㄧ提,这个月初 (2018 年 8 月),长江存储发表其称之为 Xtacking 的突破性技术。它将为其 3D NAND 闪存带来前所未有的 I/O 高性能、高存储密度,以及更短的产品上市周期。依据其新闻稿,Xtacking 技术只需一个处理步骤就可通过数百万根金属 VIA (Vertical Interconnect Accesses,垂直互联通道) 将二片晶圆键合接通电路 (注意是二片晶圆而非二颗晶粒),其中一片晶圆是负责数据 I/O 及存储单元操作的外围电路,另一片晶圆则是 3D NAND 存储单元。这样的方式有利于 I/O 及控制电路以及 3D NAND Flash 各自选择其最合适的先进逻辑工艺,这 Xtacking 技术可以让其 NAND I/O 速度得以提升到 3.0Gbps (目前世界上最快的 3D NAND I/O 速度的目标值是 1.4Gbps), 与 DRAM DDR4 的 I/O 速度相当,这即将量产的国产 3D NAND 闪存值得期待。

相关问答

nand 和tlc的区别?区别就是两者所表达的中文意思是不一样,具体的不同如下NAND是一种比硬盘驱动器更好的存储设备,在不超过4GB的低容量应用中表现得尤为明显。TLC:Trinary-Leve...

2019 NAND存储 市场降价喜人,闪存制造商们是否会考虑减产提价?作为一个“周期性市场”,NAND闪存制造商们经历了多次的“繁荣与萧条”。尽管对于消费者来说,现阶段存储市场的价格走势很是喜人。但是对于制造商们来说,为了...