「收藏」Flash闪存颗粒和工艺知识深度解析

[收藏] Flash闪存颗粒和工艺知识深度解析

原创: Hardy 架构师技术联盟 5天前

Wafer即晶圆,是半导体组件“晶片”或“芯片”的基材,从沙子里面高温拉伸生长出来的高纯度硅晶体柱(Crystal Ingot)上切下来的圆形薄片称为“晶圆”。采用精密“光罩”通过感光制程得到所需的“光阻”,再对硅材进行精密的蚀刻凹槽,继续以金属真空蒸着制程,于是在各自独立的“晶粒”(Die)上完成其各种微型组件及微细线路。对晶圆背面则还需另行蒸着上黄金层,以做为晶粒固着(Die Attach) 于脚架上的用途。

以上流程称为Wafer Fabrication。早期在小集成电路时代,每一个6吋的晶圆上制作数以千计的晶粒,现在次微米线宽的大型VLSI,每一个8吋的晶圆上也只能完成一两百个大型芯片。我们NAND Flash的Wafer,目前主要采用8寸和12寸晶圆,一片晶圆上也只能做出一两百颗NAND Flash芯片来。

NAND Flash Wafer

Wafer的制造虽动辄投资数百亿,但却是所有电子工业的基础。晶圆的原始材料是硅,而地壳表面有用之不竭的二氧化硅。二氧化硅矿石经由电弧炉提炼,盐酸氯化,并经蒸馏后,制成了高纯度的多晶硅,其纯度高达99.99%以上。晶圆制造厂再将此多晶硅融解,再在融液里种入籽晶,然后将其慢慢拉出,以形成圆柱状的单晶硅晶棒,由于硅晶棒是由一颗晶面取向确定的籽晶在熔融态的硅原料中逐渐生成,此过程称为“长晶”。硅晶棒再经过切段,滚磨,切片,倒角,抛光,激光刻,封装后,即成为集成电路工厂的基本原料——硅晶圆片,这就是“晶圆”。

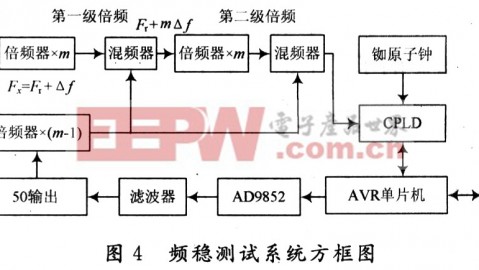

下图是NAND Flash生产简要流程:

Die 就是芯片未封装前的晶粒,是从硅晶圆(Wafer)上用激光切割而成的小片(Die)。每一个Die就是一个独立的功能芯片,它无数个晶体管电路组成,但最终将被作为一个单位而被封装起来成为我们常见的闪存颗粒,CPU等常见芯片。

什么是ink Die

在晶圆制造过程中,会对Wafer中的每个Die进行严格测试,通过测试的Die,就是Good Die,未通过测试的即为Ink Die。这个测试过程完成后,会出一张Mapping图,在Mapping里面会用颜色标记出不良的Die,故称Ink Die。

Flash芯片封装分类

目前NAND Flash封装方式多采取TSOP、FBGA与LGA等方式,由于受到终端电子产品转向轻薄短小的趋势影响,因而缩小体积与低成本的封装方式成为NAND Flash封装发展的主流趋势。

TSOP: (Thin smaller outline package )封装技术,为目前最广泛使用于NAND Flash的封装技术,首先先在芯片的周围做出引脚,采用SMT技术(表面安装技术)直接附着在PCB板的表面。TSOP封装时,寄生参数减小,因而适合高频的相关应用,操作方便,可靠性与成品率高,同时具有价格便宜等优点,因此于目前得到了极为广泛的应用。

BGA: (Ball Grid Array也称为锡球数组封装或锡脚封装体 )封装方式,主要应用于计算机的内存、主机板芯片组等大规模集成电路的封装领域,FBGA 封装技术的特点在于虽然导线数增多,但导线间距并不小,因而提升了组装良率,虽然功率增加,但FBGA能够大幅改善电热性能,使重量减少,信号传输顺利,提升了可靠性。

采用FBGA新技术封装的内存,可以使所有计算机中的内存在体积不变的情况下容量提升数倍,与TSOP相比,具有更小的体积与更好的散热性能,FBGA封装技术使每平方英寸的储存量有很大的提升,体积却只有TSOP封装的三分之一,与传统TSOP封装模式相比,FBGA封装方式有加快传输速度并提供有效的散热途径,FBGA封装除了具备极佳的电气性能与散热效果外,也提供内存极佳的稳定性与更多未来应用的扩充性。

LGA: (Land Grid Array ) 触点陈列封装,亦即在底面制作有数组状态坦电极触点的封装,装配时插入插座即可,现有227 触点(1.27mm中心距)和447 触点(2.54mm 中心距)的陶瓷LGA,应用于高速逻辑 LSI 电路,由于引线的阻电抗小,对高速LSI 相当适用的,但由于插座制作复杂,成本较高,普及率较低,但未来需求可望逐渐增加。

Flash芯片封装叠Die(Stack Die)

由于NAND Flash单颗Die的容量有限,为了实现更高的容量,需要在一个封装片内堆叠几个Die。在Wire Bond的时候,用金线互连。

目前单颗Die的容量最高的为Micron公司的MLC 4GB,目前最先进的堆叠技术可以叠8层,因此理论上MLC单颗封装片可以做到32GB。Micron公司计划在09年Q4推出此容量的封装片。

Flash芯片TSOP封装和BGA封装的内部结构

TSOP封装只需要一个引脚框架,把NAND FLASH Die的Pad打线(Wire Bond)连接到引进框架上面即可。封装技术简单,成本低。但其打线方式只能从两边打线,因此stack die就比较困难。

BGA封装与TSOP封装不同在于其采用了Substrate,用电路板来对引脚走线,因此可以进行四面打线,这样在进行叠die的时候,就变得更加容易操作。但成本会比TSOP要高。

Flash芯片封装的尺寸,一些封装方式尺寸比较:

NAND Flash出货有两种产品样式:

一种是Wafer,即晶圆出货,这种产品样式一般客户采购回去需要再测试和COB封装等,这种客户多为闪存卡大客户。

一种是封装片出货,NAND Flash目前最普遍采用的是48TSOP1的封装方式,现货市场均为TSOP的封装片。

NAND Flash按工艺可分为SLC与MLC

SLC英文全称(Single Level Cell)即单层式单元储存。SLC技术特点是在浮置闸极与源极之中的氧化薄膜更薄,在写入数据时通过对浮置闸极的电荷加电压,然后透过源极,即可将所储存的电荷消除,通过这样的方式,便可储存1个信息单元,这种技术能提供快速的程序编程与读取,不过此技术受限于Silicon efficiency的问题,必须要用较先进的流程强化技术,才能向上提升SLC制程技术。

MLC英文全称(Multi Level Cell)即多层式单元储存。Intel在1997年9月最先开发成功MLC,其作用是将两个单位的信息存入一个Floating Gate(闪存存储单元中存放电荷的部分),然后利用不同电位(Level)的电荷,通过内存储存的电压控制精准读写。MLC通过使用大量的电压等级,每一个单元储存两位数据,数据密度比较大。SLC架构是0和1两个值,而MLC架构可以一次储存4个以上的值。因此,MLC架构可以有比较高的储存密度。

TLC英文全称(Triple Level Cell)即一个单元可以存储单元可以存储3bit,因此需要8个等级的电位进行编码解码才能实现。其实TLC是属于MLC的一种。

SLC和MLC的基本特性表

Flash坏块的形成

NAND Flash的存储原理是,在写入(Program)的时候利用F-N隧道效应(Tunnel Injection隧道注入)的方法使浮栅充电,即注入电荷;在擦除(Erase)的时候也是是利用F-N隧道效应(Tunnel Release隧道释放)将浮栅上的电荷释放。

隧道注入和隧道释放的产生都需要十几伏的瞬间高电压条件,这对浮栅上下的氧化层会造成一定损伤,因此这样重复的操作(P/E Cycle)是有限的。SLC大概是100K次,MLC大概是10K次。达到读写寿命极限的时候存储单元就会出现失效,然后就会造成数据块擦除失效,以及写入失效,于是就会被标记起来,作为坏块,并将这个标记信息存放在Spare Area里面,后续操作这个Block时,需要Check一下这个信息。

Flash固有坏块

由于制造工艺的原因,通常普通的NAND FLASH从出厂开始就有坏块了,一般在2‰以下。一般芯片原厂都会在出厂时都会将坏块第一个page的spare area的第6个byte标记为不等于0xff的值。

NAND Flash的存储单元是有使用寿命的

NAND Flash的存储原理是,在写入(Program)的时候利用F-N隧道效应(Tunnel Injection隧道注入)的方法使浮栅充电,即注入电荷;在擦除(Erase)的时候也是是利用F-N隧道效应(Tunnel Release隧道释放)将浮栅上的电荷释放。隧道注入和隧道释放的产生都需要20V左右瞬间高电压条件,这对浮栅上下的氧化层会造成一定损伤,因此这样重复的操作(P/E Cycle)是有限的。SLC大概是100K次,MLC大概是10K次。

三星估算的SSD硬盘的寿命

如果每天对SSD写入4.8GB的数据,假设SSD总容量为16GB,那么,你至少需要3.34天才能对整个SSD的每个单元擦写一次;如果此SSD为擦写次数为100K的SLC单元,那么,你至少需要3.34×100K天才能使这个SSD完全失效;3.34×100K天=913年,因此16G的SSD可以使用913年 。那么,如果是MLC的话,也至少可以使用91.3年。

晶圆制程工艺发展历史

芯片制程工艺是指晶圆内部晶体管之间的连线间距。按技术述语来说,也就是指芯片上最基本功能单元门电路和门电路间连线的宽度。

主流厂商的晶圆制程工艺以及下一代制程工艺的情况,如下表。

芯片制造工艺在1995年以后,从0.5微米、0.35微米、0.25微米、0.18微米、0.15微米、0.13微米、90纳米、75纳米、65纳米一直发展到目前最新的34纳米。

一步步印证了摩尔定律的神奇。以90纳米制造工艺为例,此时门电路间的连线宽度为90纳米。我们知道,1微米相当于1/60头发丝大小,经过计算我们可以算出,0.045微米(45纳米)相当于1/1333头发丝大小。可别小看这1/1333头发丝大小,这微小的连线宽度决定了芯片的实际性能,芯片生产厂商为此不遗余力地减小晶体管间的连线宽度,以提高在单位面积上所集成的晶体管数量。采用34纳米制造工艺之后,与65纳米工艺相比,绝对不是简单地令连线宽度减少了31纳米,而是芯片制造工艺上的一个质的飞跃。

目前最先实现34nm工艺的是Intel和Micron联合投资的IM,此技术被最先应用在了NAND FLASH上面,可见NAND FLASH的制程工艺跳跃是所有IC中最快的。

晶圆技术的发展都是受生产力驱动,必须向更小的制程间距和更大的晶圆尺寸发展。制程从2.0um、0.5um、0.18um、90nm一直到目前的34nm,晶圆尺寸从最初的5英寸发展到目前的12英寸,每次更迭都是一次巨大的技术跳跃,凝聚了人类科技的结晶,也一次次印证了摩尔定律的神奇。

晶圆尺寸的大约每9年切换一次。而晶圆制程由最初的几年更迭一次,到目前的基本上每年都能更迭一次。

更多内容和“闪存技术、产品和发展趋势全面解析”全面的闪存技术电子书,请点击“了解更多”查阅。

巨头们发力先进封装

来源:内容由导体行业观察(ID:icbank)编译自semianalysis,谢谢。

ECTC 是先进封装领域首屈一指的会议,在会上会讨论一些先进封装领域我们最喜欢的一些主题,例如混合键合、共同封装光学器件等。还有一些交易和供应链细节,我们也可以专门详细介绍与这些主题相关的内容。今年有,笔者参加了 2022 年 IEEE 第 72 届电子元件和技术会议。在这里,我们将讨论的重点包括台积电的 CoWoS-R+、台积电的第四代 SoIC(3 微米间距混合键合)、英特尔和 CEA-LETI 自对准集体(collective)裸片到晶圆混合键合、三星对包括混合键合在内的monolithic vs MCM vs 2.5D vs 3D 的研究。以及SK海力士、美光和联发科等在先进封装方面的研究。台积电的 CoWoS-R+

正如大家所知道,CoWoS 是一种chip last 封装技术。CoWoS 通常是通过将有源硅dies放置在无源硅中介层之上来完成的,但这非常昂贵。因此,台积电开发了 CoWoS-R,它使用具有 RDL 层的有机基板,这是一种更便宜的技术。CoWoS-R 还没有到产品出货阶段,但有一些产品来了。我们知道的第一款此类产品来自 AMD。坦率地说,这个技术这太神奇了。台积电并没有止步于 CoWoS R,CoWoS-R+ 在这项技术上不断发展。台积电第 4 代 SoIC,实现 3 微米间距混合键合

台积电展示了他们的第 4代混合键合技术的研究,该技术可以实现每平方毫米100,000个bond pads 的成就。鉴于只有 AMD 和台积电交付了一个 SoIC 设备,很高兴看到迄今为止在某些方面取得了切实进展。该器件在 17 微米与第一代 SoIC 能够实现的 9 微米相比相助放松。英特尔和 CEA-LETI的Collective Die to Wafer混合键合

我们知道,晶圆上芯片(Die on wafer )的精度远低于晶圆上晶圆(wafer on wafe)键合。它也慢得多。例如,尽管 Besi 声称每小时放置 2,000 个die,即使到了 1 微米的精度,吞吐量仍能降至每小时放置 1,000 个芯片以下。另一方面,晶圆上的晶圆(wafer on wafe)键合也存在许多与无法进行异质集成以及无法在键合步骤之前对die进行bin/test有关的问题。Collective Die to Wafer允许比芯片到晶圆(die to wafer)键合更高的精度和吞吐量,同时还提供test、bin和实现异构集成的能力。英特尔和 CEA-LETI 将Collective Die to Wafer与自对准技术相结合,实现了 150 纳米的平均未对准(mean misalignment,比die to wafer更准确)并具有更高的吞吐量。自对准技术非常酷。他们利用水滴的毛细作用力在修改后的拾取和放置工具将其快速但不太准确地放置在所需位置后使对齐更加准确。随着水的蒸发,产生直接键合,无需任何其他中间材料。然后,键合晶片进入标准退火步骤,加强键合。三星 Monolithic vs MCM vs 2.5D vs 3D,包括混合键合

三星在面积和功率方面对先进封装的成本进行了非常有趣的研究。他们比较了两种主要的设计类型,一种是带宽受限的 (HPC/AI),一种是延迟受限的 (CPU)。SK 海力士 Wafer On Wafer 混合键合 DRAM

SK 海力士介绍了他们对晶圆混合键合工艺的研究。用于先进封装的晶圆键合技术已经非常普遍。它用于索尼、三星和 Omnivison 的 CMOS 图像传感器。YMTC 的XStacking 技术也在 NAND Flash 中使用它。Graphcore 和 TSMC 在他们的 BOW 芯片中也使用了它。SKHynix 也将在其 16 层 HBM堆栈中使用混合键合。SKHynix 没有直接说明产量,但他们似乎非常希望将这项技术商业化。ASE 共封装光学器件

从技术角度来看,ASE 所展示的并不是那么具有开创性,但对投资者是有影响的。这是因为在过去,主要的 OSAT 都远离光网络产品。在我们看来,这项研究对我们普遍喜欢的像 Fabrinet 这样的公司不利。话虽如此,这只是研究,市场动向更为重要。无论如何,如果 ASE 正在研究这个,他们可能也会试图获得份额。现在来看看 ASE 介绍的内容。超薄die的 Xperi Die Handling

在大多数混合键合中,芯片必须非常薄。在即将推出的 16 层 HBM 的情况下,这甚至可以达到 30 微米的数量级,不到人类头发厚度的一半。而硅片非常脆弱,因此无法正常提起。因此,Xperi 展示了使用伯努利夹具(Bernoulli grip )提起die的研究,该夹具使用具有低静压的高速气流以在没有物理接触的情况下粘附到物体上。然后夹具将die放置到另一个die上,精度为 1 微米或更小。这篇论文有很多关于die翘曲和处理的细节。这里没有什么突破性的东西,但我们只是认为这是处理超薄die的一种很酷的机制。Tokyo Electron Wafer on Wafer Hybrid Bonding

世界最大的晶圆代工厂中在晶圆对晶圆(wafer-on-wafer )混合键合工具和工艺流程的重大胜利。虽然我们不知道这项研究是否会商业化,但我们认为这是另一种有趣的晶圆处理技术。晶圆太薄以至于松软,当您将其降低以进行键合时,可能会滞留空气,从而影响产量。Tokyo Electron 提出了一种避免这种情况的方法。这是研究,而不是他们当前键合工具的过程。索尼领先的 1 微米间距混合键合

索尼继续展示了为什么他们是混合键合领域的领导者。他们于 2017 年首次在大批量产品中交付该技术。他们目前每年交付数百万个 CMOS 图像传感器,采用 6.3 微米间距混合键合,堆叠 3 个裸片,而其他人的间距和体积要小得多。索尼的产品完全是晶圆对晶圆的混合键合。今年索尼推出了 1 微米间距面对面混合键合和 1.4 微米面对面混合键合。索尼目前使用面对面和面对面的混合键合。AMD Zen 3 上的 V-Cache SoIC 混合键合

AMD 重申了很多东西,但也有一些新东西。此外需要提醒一下的是,AMD 的 V-Cache 混合键合和elevated扇出桥的首席工程师离开了 AMD ,加盟了微软。我们对微软芯片的未来感到兴奋,因为他们已经从整个行业招聘了大量人才。联发科网络 SOC 可靠性

联发科发表了一篇题为“高性能计算应用的高密度扇出封装的可靠性挑战”的论文。没有说的是,这是联发科通过其定制 ASIC 部门在中国销售的用于网络应用的真正芯片。★ 点击文末【阅读原文】,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第3065内容,欢迎关注。

晶圆|集成电路|设备|汽车芯片|存储|台积电|AI|封装

相关问答

深科技是存储芯片概念股吗?深科技是内存芯片封测概念股。6月17日消息,深科技截至下午三点收盘,该股跌0.71%,报11.11元;5日内股价上涨0.09%,市值为173.38亿元。核心数据:2021年公司...

emmc结构和工作原理?eMMC的结构eMMC结构由一个嵌入式存储解决方案组成:标准MMC封装接口主控制器(控制芯片)快闪存储器设备(NANDFlash芯片)原理:这...eMMC的结构eMMC....

flash 叠化名词解释?Flash是由macromedia公司推出的交互式矢量图和Web动画的标准,由Adobe公司收购。做Flash动画的人被称之为闪客。网页设计者使用Flash创作出既漂亮又可改变...

半导体如此火爆,细分领域如何?有哪些实质性业务的上市公司?你好,我是猴子的棒子,一个泛科技领域的创作者。很高兴能回答您的问题。首先,我们看一下半导体行业从上游到中游的整个过程中会涉及到的产业链,半导体的下游...

dram是什么概念股?dram是存储概念股。相关股票有:太极实业:海力士是以生产DRAM、NANDFlash和CIS非存储器产品为主的半导体厂商,目前在韩国有一条8英寸晶圆生产线和两条12...d...

朗科科技有芯片业务吗?朗科科技有芯片业务,是其主要的业务之一。朗科科技是一家集成电路设计公司,其主要业务是设计和销售各种类型的集成电路芯片。朗科科技的芯片业务主要包括以...

FLASH 3.0和2.0有什么区别?as2的面向对象虽然不全面,但是却是首次将OOP带到了FLASH,而AS3是一个完全基本OOP的标准化面向对象语言,最重要的就是as3不是as2的简单升级,而完全是两种思想...

flash 的4ce 8ce什么意思?4c8表示的是4核8线程,这里面的c是core的缩写,也就是核心的意思。4核比较好理解,指的是在1个CPU上有4个CPU核心,更准确的说,是指在一个CPU封装上有4个物理...

esp12e和esp12f区别?ESP12E和ESP12F都是乐鑫公司(EspressifSystems)生产的WiFi模块,用于无线通信和物联网应用。它们的区别在于:1.封装类型:ESP12E采用LGA封装,而ESP12F采...

东芝如何布局5-Bit-per-Cell Flash SSD?近日召开的国际闪存技术峰会(FlashMemorySummit)上,东芝公布的内容干货满满。不仅凭借着最新推出的XFMExpress标准赢得了今年的“BestofShow”(展会最佳)...