TMS320C6678 DSP + Xilinx Kintex-7 FPGA开发板硬件接口资源图解分享

本文主要介绍硬件接口资源以及设计注意事项等内,其中测试的应用板卡为TMS320C6678DSP + Xilinx Kintex-7 FPGA核心板,它是一款基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP与Xilinx Kintex-7 FPGA处理器设计的高端异构多核评估板,由核心板与底板组成。核心板内部DSP与FPGA通过SRIO、EMIF16、I2C通信总线连接。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

本期测试时候,需要注意,TMS320C6678+Kintex-7核心板的DSP端IO电平标准一般为1.8V,FPGA端的IO电平一般不超过3.3V,当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。

核心板DSP端的IO电平标准一般为1.8V,FPGA端的IO电平一般不超过3.3V,当外接信号电平与IO电平不匹配时,中间需增加电平转换芯片或信号隔离芯片。按键或接口需考虑ESD设计,ESD器件选型时需注意结电容是否偏大,否则可能会影响到信号通信。

图 1 TL6678F-EasyEVM硬件资源框图

图 2 TL6678F-EasyEVM硬件资源框图

SOM-TL6678F核心板

SOM-TL6678F核心板板载DSP、FPGA、CPLD、ROM、RAM、晶振、电源、LED等硬件资源,并通过工业级高速B2B连接器引出IO。核心板硬件资源、引脚说明、电气特性、机械尺寸、底板设计注意事项等详细内容,请查阅《SOM-TL6678F核心板硬件说明书》。

图 3 核心板硬件框图

图 4

图 5

B2B连接器

评估底板采用4个申泰(Samtec)公司工业级高速B2B连接器,共720pin,间距0.5mm,合高5.0mm。

其中2个180pin公座B2B连接器(CON0A、CON0B),型号BTH-090-01-L-D-A-K-TR,高度4.27mm。2个180pin母座B2B连接器(CON0C、CON0D),型号BSH-090-01-L-D-A-TR,高度3.25mm。B2B连接器单端最高通信速率为18Gbps,差分最高通信速率为19Gbps。

图 6

图 7

电源接口

CON19为12V5A直流输入DC-005电源接口,外径5.5mm,内径2.1mm。SW8为电源开关。

图 8

图 9

图 10

设计注意事项:

VDD_12V_BRD通过LM2596S-ADJ(DC-DC降压芯片)输出VDD_9V_BRD供核心板使用。VDD_9V_BRD(VDD_9V_SOM)在核心板内部未预留总电源输入的储能大电容,底板设计时请在靠近B2B连接器位置放置储能大电容。VDD_3V3_BRD主要为核心板板载FPGA提供BANK电源,以及为评估底板其他外设供电。图 11

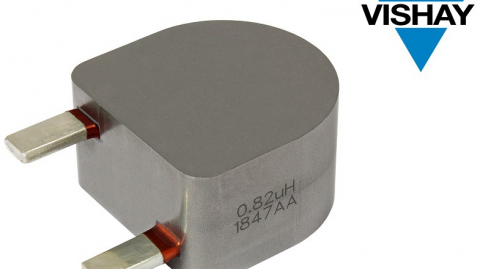

2.5V电源设计

2.5V电源主要为核心板板载FPGA提供BANK电源,以及为评估底板SGMII电路供电。

图 12

图 13

BANK电压配置电路

核心板内部已将BANK 0、BANK 14、BANK 16电平配置为1.8V,同时将BANK 33、BANK 34电平配置为1.5V。评估底板已将VDD_3V3_BRD转换为1.8V和1.5V输出,可用于灵活配置BANK 12、BANK 13、BANK 15供电,评估底板已将BANK 32电平配置为1.8V。

图 14

图 15

J1为BANK电压配置接口,可通过跳线帽灵活配置BANK 12、BANK 13、BANK 15供电为1.5V、2.5V或3.3V。

注意:切勿使用跳线帽将J1的第1、3、5引脚进行短接。

图 16

图 17

LED

评估底板具有LED0、LED1、LED2、LED3、LED4、LED5共6个LED。

LED0为电源指示灯,系统上电后默认点亮。

图 18

LED1、LED2为DSP端用户可编程指示灯,默认低电平点亮。

图 19

图 20

LED3、LED4、LED5为FPGA端用户可编程指示灯,默认高电平点亮。

图 21

JTAG接口

评估底板由同一组DSP JTAG信号引出2个调试接口CON8和CON7,二者不可同时使用。

CON8为DSP端TI Rev B JTAG仿真调试接口,采用14pin简易牛角座连接器,间距2.54mm,可适配创龙科技的TL-XDS100V2、TL-XDS200仿真器和TL-XDS560V2仿真器。

图 22

图 20

CON7为DSP端TI 60pin MIPI高速仿真接口,可适配创龙科技TL-XDS560V2仿真器。

图 21

图 23

CON10为FPGA JTAG仿真调试接口,采用14pin简易牛角座连接器,间距2.0mm,可适配创龙科技的TL-DLC10下载器。

图 24

图 24

设计注意事项:

CON8接口引脚信号电平为3.3V。CON10接口引脚从BANK 0引出,电平为3.3V。底板设计时,若DSP端JTAG总线仅引出测试点,通过飞线方式连接仿真器时,需将仿真器端的TDIS引脚接到底板的数字地,否则仿真器将无法识别到设备。BOOTSET启动选择拨码开关

SW6为5bit启动方式选择拨码开关,由核心板板载CPLD的SYS_BOOTSET[1:5]引脚引出。可通过CPLD控制DSP端及FPGA端系统启动配置。

图 25

图 26

评估板支持DSP_NO BOOT、DSP_IBL NOR、DSP_IBL NAND、DSP_NOR和DSP CFG FPGA等启动方式,具体说明如下。

表 1

启动模式

拨码开关(1~5)

说明

DSP_NO BOOT

000XX

DSP Debug模式

DSP_IBL NOR

100XX

DSP从EEPROM启动IBL,引导SPI FLASH用户程序

DSP_IBL NAND

110XX

DSP从EEPROM启动IBL,引导NAND FLASH用户程序

DSP_NOR

111XX

DSP从SPI FLASH启动IBL,引导SPI FLASH用户程序

DSP CFG FPGA

XXXX1

FPGA配置为Slave Serial模式,此时DSP可通过SPI总线在线加载FPGA程序

-

XXXX0

FPGA配置为Master SPI模式,此时FPGA可进行程序在线加载、固化并离线启动

备注:BOOTSET启动选择拨码开关ON为1,相反为0,X代表任意值。

设计注意事项:

SYS_BOOTSET[1:3]为DSP端启动配置设置位。由于DSP端BOOTSET引脚与GPIO信号存在复用关系,如使用GPIO外接设备,请保证DSP在上电初始化过程中BOOTSET引脚电平不受外接设备的影响,否则将会导致DSP无法正常启动。

SYS_BOOTSET[4]为DSP PCIe接口同源时钟及非同源时钟选择设置位。板载DSP PCIe接口支持非同源时钟模式和同源时钟模式,核心板引出SYS_BOOTSET[4]引脚进行选择配置,0为非同源模式,1为同源模式。其中非同源时钟模式采用板载CDCM610002时钟芯片输出的100MHz时钟源,同源时钟模式采用评估底板PCIe接口输入的时钟源。

SYS_BOOTSET[5]为FPGA端启动配置设置位。0为Master SPI模式,此时FPGA可进行程序在线加载、固化并离线启动。1为Slave Serial模式,此时DSP可通过SPI总线在线加载FPGA程序。

KEY

评估底板包含1个系统复位按键FULL RESET(KEY2)。DSP端包含1个用户输入按键DSP USER1(SW2)、1个不可屏蔽中断按键DSP NMI(SW1)、1个系统复位按键DSP WARM RESET(KEY1)。FPGA端包含1个程序复位按键PROG(SW5)、2个用户测试按键FPGA USER1(SW3)和FPGA USER2(SW4)。

图 27

图 28

设计注意事项:

KEY2按键控制由核心板CPLD引出的SYS_nRESET复位信号,该信号拉低时可使核心板DSP和FPGA重新上电,无需使用时应上拉10K电阻到核心板引出的VDD_1V8_REF电源。

图 29

KEY1按键控制DSP_RESETZ信号,DSP_RESETZ为DSP的WARM RESET功能引脚,无需使用时应上拉10K电阻到核心板引出的VDD_1V8_REF电源。

图 30

SW1按键控制DSP_NMI信号,DSP_NMIZ为DSP端的不可屏蔽中断功能引脚,无需使用时应上拉5K电阻到VDD_1V8_BRD电源。

图 31

评估底板通过GPIO_00引出用户输入按键SW2,上拉5K电阻到VDD_1V8_BRD。

图 32

SW5按键控制FPGA_PROG信号,FPGA_PROG信号为核心板FPGA端的复位引脚,无需使用时请悬空处理。

图 30

勘误:FPGA_PROG信号引脚上拉电压错误说明

存在问题:FPGA_PROG信号引脚连接至BANK 0,BANK 0电压已配置为1.8V,而在原理图中错误上拉至3.3V,实际设计应上拉至1.8V。

使用说明:底板设计时,请将FPGA_PROG信号引脚上拉至1.8V。

评估底板通过FPGA端的IO_L23P_T3_34引出用户输入按键SW3,通过FPGA端的IO_L23N_T3_34引出用户输入按键SW4,引出信号均上拉5.1K电阻到VDD_1V5_BRD 。

图 31

串口

评估板通过CP2105芯片将DSP端的UART转成Micro USB接口,作为DSP端的调试串口使用。

评估板通过CP2105芯片将FPGA端的IO_L1P_T0_16(定义为UART的RX)、IO_L1N_T0_16(定义为UART的TX)转成Micro USB接口,作为FPGA端的调试串口使用。

图 32

图 33

FAN供电接口

CON2为散热器风扇电源(FAN)接口,采用3pin排针端子方式,间距2.54mm,12V供电,可通过DSP端控制散热器风扇的运转。

图 34

图 35

设计注意事项:

风扇电路及风扇接口不支持调速功能,不建议使用PWM模式控制风扇开关电路。

Ethernet接口

CON3为DSP ETH0千兆网口,CON4为DSP ETH1千兆网口。TMS320C6678内部集成2个GMAC控制器,支持2路SGMII千兆以太网。

图 36

图 40

图 41

设计注意事项:

SGMII总线DSP_SGMII0_RXP/DSP_SGMII0_RXN、DSP_SGMII1_RXP/DSP_SGMII1_RXN已在核心板内部串联100nF耦合电容,底板设计时无需再次串联耦合电容。

88E1111收发器的1.2V电源由TPS563200DDCT(U33)芯片输出、2.5V电源由TPS563200DDCT(U32)芯片输出。

勘误:网口电路耦合电容设计

存在问题:评估板DSP ETH0和DSP ETH1网口通信功能正常,但SGMII0和SGMII1总线未按照规范设计耦合电容。SGMII总线DSP_SGMII0_RXP/DSP_SGMII0_RXN、DSP_SGMII1_RXP/DSP_SGMII1_RXN已在核心板内部串联100nF耦合电容,但底板重复串联耦合电容。SGMII总线DSP_SGMII0_TXP/DSP_SGMII0_TXN、DSP_SGMII1_TXP/DSP_SGMII1_TXN未在核心板内部串联100nF耦合电容,底板亦未在靠近PHY芯片处串联100nF耦合电容。

使用说明:底板设计时,SGMII总线DSP_SGMII0_RXP/DSP_SGMII0_RXN、DSP_SGMII1_RXP/DSP_SGMII1_RXN无需再次串联耦合电容,但DSP_SGMII0_TXP/DSP_SGMII0_TXN、DSP_SGMII1_TXP/DSP_SGMII1_TXN总线需在靠近PHY芯片处串联100nF耦合电容。

PCIe接口

CON5为DSP端PCIe Gen2接口,包含双通道链路,每通道最高通信速率5Gbps,金手指连接方式,默认作为EP(End Point)模式使用。

图 37

图 38

设计注意事项:

评估底板PCIe接口的支持模式如下表所示:

表 2

PCIe模式

典型对接设备

核心板

RC(同源时钟)

连接PCIe网卡

不支持

RC(非同源时钟)

连接DSP、FPGA

支持

EP(同源时钟)

连接ARM

不支持

EP(非同源时钟)

连接ARM

支持

DSP PCIe支持同源时钟模式和非同源时钟模式,可通过评估底板SW6拨码开关的SYS_BOOTSET[4]引脚进行配置,1为同源模式,0为非同源模式。

PCIE_TX1N/TX1P和PCIE_TX2N/TX2P线路需靠近CON5放置100nF的AC耦合电容。

SFP+接口

CON13(SFP1)、CON14(SFP2)为FPGA端SFP+接口,支持SFP+(10G)光模块。CON13接口使用GTX Quad 116的MGTXRX_0、MGTXTX_0引脚,CON14接口使用GTX Quad 116的MGTXRX_1、MGTXTX_1引脚。

图 39

图 40

FMC接口

CON15、CON16为FMC LPC接口,各包含一对GTX信号引脚,可配套创龙科技的视频输入/输出、高速AD/DA等FMC模块使用。

图 41

图 42

图 43

勘误:FMC GTX速率稳定性问题

存在问题:FMC GTX在5Gbps速率时可稳定运行,在8Gbps或以上速率时眼图开口较小,可能存在稳定性问题。硬件等长、阻抗等暂未发现异常,GTX时钟亦正常,可能是由于PCB Layout的其他问题导致。

使用说明:可通过软件进行时序优化。

XADC接口

评估板通过CO18排母接口(2x 6pin规格,间距2.54mm)引出FPGA端1对专用模拟差分输入XADC_VN_IN和XADC_VP_IN。

图 44

图 50

设计注意事项:

unipolar模式支持0~1V输入,bipolar模式支持-0.5~0.5V输入,输入信号请勿超过以上范围,否则可能会损坏核心板。

拓展IO信号接口

CON6通过IDC3简易牛角座引出了DSP端EMIF16拓展信号,2x 25pin规格,间距2.54mm。

图 51

图 45

CON12通过IDC3简易牛角座引出了DSP端SPI、TIMER、GPIO拓展信号,2x 25pin规格,间距2.54mm。

图 46

图 47

CON17为欧式公座连接器,3x 16pin规格,间距2.54mm,引出FPGA端的IO拓展信号。

图 48

图 49

设计注意事项:

由于DSP端的CON6、CON12扩展接口存在IO复用情况,如需使用请注意功能之间的相互影响,详情可查阅《SOM-TL6678F核心板硬件说明书》以及CPU数据手册。

TMS320C6678 DSP的加载引导研究

摘 要 : 德州仪器公司(TI)推出的八核DSP芯片TMS320C6678是基于Keystone架构的高性能DSP器件,在高性能信号处理市场中得到了广泛应用。主要研究了TMS320C6678程序的加载,把TMS320C6678提供的几种加载模式按照实际应用和方便理解分成一次加载和二次加载,分别对一次加载和二次加载进行了研究和比对,最终为不同需求的加载提供了有效的参考。

0 引言

DSP芯片自从问世以来,以其低成本、低功耗、高性能的优点得到了广泛应用。作为TI最新推出的八核DSP芯片TMS320C6678[1-2],更是在高性能信号处理市场中占据大量市场份额[3]。为了适应市场的需求,其发展方向也在不断地发生变化。嵌入式系统的迅猛发展,使得TI公司在其开发软件CCS中开发DSP芯片的文件格式也在向兼容嵌入式系统的方向发展。在较新的CCS5.2版本中调试DSP6000系列程序生成的可执行文件格式最终过渡到了完全兼容Linux嵌入式系统的ELF文件格式[4]。由于DSP内部存储器比外部存储器的存取速度要快得多,但是内部存储器RAM中的数据是掉电易失的,因此DSP一般会在上电时通过固化到内部的ROM中的一段代码把外部存储器中的程序拷贝到内部RAM(具体到TMS320C6678是L2SRAM)中并运行,这段固化到ROM中的代码就叫RBL(ROM Bootloader)。外部存储器一般使用Flash、EEPROM等掉电非易失的材质。Flash存储容量大、价格便宜,在工程项目中得到了的广泛应用。因此,研究DSP的加载[5-6],研究怎样快捷方便地把ELF文件格式的调试程序代码烧写到外部存储器中,并在DSP上电时使用Bootloader把程序代码拷贝到内部存储器中被DSP正确识别并运行,这是很有意义的。

1 一次加载

目前关于TMS320C6678加载的文档资料较少而且讲得很凌乱,在经过研读其各种手册并且经过实际项目的检验,把TMS320C6678所提供的加载模式按照以下文章中提供的分类方法将各种模式分类会更容易理解。TMS320C6678的加载模式主要可以分为一次加载和二次加载。其中一次加载主要是兼容以前版本的DSP加载方式,主要特点是占用存储空间小,转换过程复杂;二次加载是较新的加载方式,主要特点是占用存储空间稍大一些,但是整体操作流程简单。

本文所使用的硬件是TI公司生产的DSP6678EVM开发板[7-8],所使用的软件是TI公司提供的CCS、MCSDK开发套件中的IBL(Intermediate Bootloader)和Flash烧写工具[9]。本文中定义一次加载为在DSP开机加载时使用RBL搬移外部存储器中的代码。因为IBL比RBL最主要的一个优势是搬移代码时不需要提前进行格式转换,可以自动识别和搬移ELF文件的格式。DSP TMS320C6678的一次加载同TI公司的较前期的产品6000系列和5000系列类似,主要是因为固化到核内部ROM中的Bootloader都大同小异,但是TMS320C6678 PG1.0的锁相环在ROM Bootloader中不能被锁定[10],因此在EVM6678开发板上FPGA首先会强制DSP TMS320C6678 boot时先把I2C EEPROM的0X51中的IBL拷贝到L2SRAM并运行IBL,配置好锁相环,然后再执行一次加载。IBL主要包含了参数的配置部分和不同存储器的代码搬移部分。也就是说一次加载运行了IBL代码的前一部分,配置完参数就重新跳转到RBL进行代码搬移的工作。所以烧写到外部存储器中的代码应该能让RBL识别,因此需要有一个格式转换的过程,然后再烧写到外部存储器中。

一次加载的过程如图1所示。开发板在上电之后,首先开发板上的FPGA采样boot模式的拨码开关,然后FPGA强制DSP从I2C总线的0x51地址启动拷贝IBL到L2SRAM,执行IBL,配置好锁相环,IBL从FPGA寄存器中读bootmode的值,如果不是二次加载,IBL把读到的bootmode值写入到DEVSTAT寄存器,如果是PCIE一次加载还需要配置PCIE工作环境,然后就在IBL中等待PCIE boot完成,如果不是PCIE boot而是从I2C的0x50 boot,IBL会直接从0X50 boot,否则IBL会直接跳入到RBL的起始位置并根据DEVSTAT寄存器的值进行相应的boot。

在一次加载中,想要boot的代码首先要先进行格式转换,转换成RBL可以识别的代码,同时要满足外部存储器件烧写格式的需求。使用TI提供的工具自己制作一个工具链就能完成[11-12],如图2所示。

rmd文件里面包含一些对Hex.6x操作的指令,首先用hex.6x把程序中有效数据按照指令剥离出来得到btbl文件,然后经过两个小工具得到ccs文件只包含各个段的内容,并不包含boot参数的任何内容,因此要给其配置参数头,由于RBL只识别大端模式,还要进行一次大小段的转换。最后把生成的文件烧写到外部存储器后断电,把boot开关拨到相应的位置,上电boot。

2 二次加载

查看IBL的源代码可以知道IBL主要被设计为两段Bootloader,即iblinit.c和iblmain.c,两个文件都有main函数,其中iblinit.c主要用来初始化锁相环,iblmain.c主要处理二次加载启动。TMS320C6678在上电boot时在IBL中读出bootmode是二次加载后会直接把该加载模式中对应的外部存储器中的代码搬移到L2SRAM并运行这段代码,完成boot。TMS320C6678提供的二次加载有I2C NOR Flash加载、I2C NAND Flash加载、I2C TFTP加载3种模式。

因为二次加载时是使用IBL进行代码搬移,所以二级加载时不需要格式转换,只需要把调试的.out文件后缀名改成.bin,使用MCSDK提供的烧写工具烧写到Flash中即可,IBL搬移代码时能自动识别。对比一次加载,二次加载不需要自己编写工具链,操作简便,虽然相比一级加载,ELF格式文件里面有一些无用信息会使得占用存储空间稍大一些,但是现在Flash存储空间足够大,价格便宜,因此二级加载相对更方便。

二次加载中的IBL代码其实就是一次加载中的放在外部存储器中的程序代码,所以使用二次加载前,要先把IBL代码按照一次加载的要求转换文件格式烧写到外部存储器件中。

3 结论

DSP TMS320C6678有一次加载和二次加载之分,最主要区别就是是否使用IBL中的搬移代码的功能,如果没有使用,则要对代码进行格式转换。如果外部存储器空间小对存储空间要求较高,建议使用一次加载;如果外部存储空间较大,推荐使用二次加载,过程简单。

参考文献

[1] Texas Instruments Corp. TMS320C6678 multicore fixed and floating-point digital processor user guide[EB/OL]. [2012-02-XX](2015-08-02). http://www.ti.com/lit/ds/symlink/tms320c6678.pdf.

[2] Texas Instruments Corp. TMS320C66x DSP corepac user guide[EB/OL]. [2013-06-XX](2015-08-02). http://www.ti.com/lit/ug/sprugw0c/sprugw0c.pdf.

[3] 庞娜,徐平江.基于多核DSP的MIMO雷达信号处理的实现[J].电子技术应用,2014,40(9):4-6,13.

[4] Texas Instruments Corp. Keystone architecture DSP bootloader user guide[EB/OL]. [2013-06-XX](2015-08-02). http://www.ti.com/lit/ug/sprugy5c/sprugy5c.pdf.

[5] 张乐年,关榆君.基于TMS320C6678的多核DSP加载模式研究[J].电子设计工程,2013,21(24):166-169,173.

[6] 沈发江.基于以太网的DSP网络加载技术研究[J].微型机与应用,2013,32(7):58-60,63.

[7] Texas Instruments Corp. TMDSEVM6678L EVM technical reference manual version 2.0[EB/OL].[2012-04-XX](2015-08-02). http://www.docin.com/p-673366367.html.

[8] Texas Instruments Corp. TI TMS320C6678 EVM board rev. 3A[EB/OL].[2012-04-XX](2015-08-02).http://www.ti.com/lit/df/tidrtt2/tidrft2.pdf.

[9] Texas Instruments Corp. BIOS MCSDK 2.0 user guide[EB/OL].[2015-04-XX](2015-08-02). http://processors.wiki.ti.com/index.php/BIOS_ MCSDK_2.0_User_Guide.

[10] Texas Instruments Corp. TMS320C6678 multicore fixed and floating-point digital signal processor silicon revision 1.0, 2.0[EB/OL]. [2015-05-XX](2015-08-02). http://www.ti.com/lit/er/sprz334h/sprz334h.pdf.

[11] Texas Instruments Corp. TMSC6000 assembly language tools v7.6 user′s guide[EB/OL]. [2014-04-XX](2015-08-02). http://www.ti.com/lit/ug/spru186x/spru186x.pdf.

[12] TMS320C6000 optimizing compiler v7.4 user′s guide[EB/OL]. [2012-06-XX](2015-08-02). http://www.ti.com/lit/ug/spru187v/spru187v.pdf.

相关问答

C6678 可以用GPINT8同时中断多核吗?当然,GPIOINT8实质上是一个片级事件,任何一个核想要响应这个事件(或者说在这个事件发生时产生中断),都必须对该核作INTC配置。各个核的INTC配置是完全独立的...