基于Flash控制器的FPGA在线加载功能设计

近些年来,由于其灵活可配置性及成本的降低,现场可编程门阵列(Field Programmable Gate Array,FPGA)在嵌入式系统中应用越来越广泛,不论产品的初期研发或是后期维护都不可避免地需要频繁更新FPGA程序。传统的JTAG方式更新FPGA程序的方式是通过开发软件将需固化的文件写入Nor Flash器件。当系统很复杂且需要更新的FPGA数量较多时,JTAG方式更新FPGA程序则费时费力且还需拆结构。若在FPGA内部通过逻辑代码搭建一Flash控制器实现对Flash器件的读写操作,即可并行实现系统内每片FPGA对配置文件的在线更新,大大缩短程序固化时间。本文依托于Xilinx公司的FPGA和Spasion公司的Nor Flash,详细介绍了Flash控制器设计和在线加载功能的实现方法。

1 FPGA配置方式

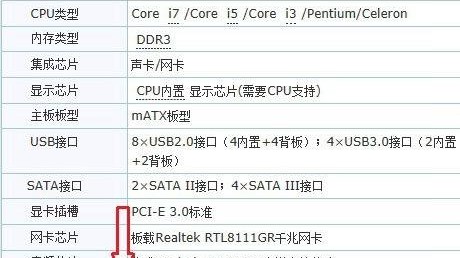

以Xilinx Virtex6 系列FPGA为例,对配置文件的加载方式有串行Flash、并行Flash、JTAG方式等,其中最常用的是并行Flash方式(Byte Peripheral Interface Parallel Flash Mode,BPI),其配置模式如图1所示。

一种实际的FPGA与Nor Flash硬线连接方式如图2所示。

无论是通过JTAG方式还是通过软件操作实现程序更新,都是通过控制这些读写使能信号及地址线实现配置文件的写入,FPGA掉电重启之后再从Flash取出配置数据从而实现加载。本文提出的FPGA在线更新程序的方式则是通过FPGA控制逻辑驱动Flash的数据和地址,从而为多块FPGA并行更新程序的实现提供了前提。

2 Flash控制器设计

Flash器件的基本操作包括读、写、擦除等,这些操作都是通过向相应的命令寄存器写入特定的指令来实现的,这些指令的写入通过操作与FPGA相连的片选信号(ce_n)、写使能信号(we_n)、读使能信号(oe_n)、地址总线(addr[23:0])和数据总线(dq[15:0])实现。

以目前市场上常用的Spasion公司的S29GL-P系列Nor Flash为例,通过FPGA实现的控制器外部接口如图3所示。

其中,start信号用于启动控制器模块对Flash器件实现读写操作,在启动之前,须先告知Flash配置文件大小和配置文件在Flash存储空间的首地址;data_req、data_in和rd_data_count信号用于与一前端FIFO实现数据交互,配置文件先缓存到FIFO中,然后由控制器负责取出并写入Flash器件;config_status信号用于指示程序更新是否完成。

该Flash控制器按时间上的先后顺序分别实现了对Flash器件的读ID、擦除和写缓冲操作,下面将分别进行简要叙述。

每次对Flash进行基本的读写操作之前,会对Flash芯片进行读ID操作以检验器件的好坏,读ID涉及的主要操作为向特定寄存器写入相应的解锁指令,然后再进行多操作读出相应的寄存器值,其时序图及读结果如图4所示。

确认了芯片ID无误,即可进行正确访问,首先对Flash芯片进行擦除操作。Flash芯片擦除可分为两种:整片擦除和扇区擦除。由于实际使用时并未用到整块Flash存储空间,而是根据配置文件的大小选择合适的扇区大小存储配置文件,所以设计中采用的是扇区擦除方式,时序如图5所示。

当成功写入擦除操作指令之后,芯片会进入一个较长的周期等待擦除操作的完成,该期间无法对芯片进行复位之外的其他操作。

完成了擦除操作之后,即可向Flash写入配置数据,其对应的写缓冲时序如图6所示。

擦除和读写的过程中,地址将进行自动累加且起始地址可变。Flash的写操作可为单字写和缓冲写两种,由于缓冲写最大一次可向Flash写入32个字,为了最大化写入速度,选择缓冲写方式;Flash的读操作分为单字读和按页读两种,由于Flash读数据速率较高且系统对读速率没有太高要求,本文选择单字读方式。

3 工程应用及性能测试

以一实际项目工程为例,系统中具有10块FPGA进行程序更新,其在线加载功能系统架构如图7所示。

系统主控CPU运行在Linux系统下,CPU通过以太网与远程计算机进行通信调试,同时通过PCIE或SRIO高速总线向每块FPGA下发配置数据,最后再由Flash控制器完成数据的写入。如前文所述,一次写缓冲操作的数据量为32个字,而配置文件的大小有可能不是32个字的整数倍,所以还需要应用软件对配置文件进行补齐操作。单个FPGA在线加载流程简要叙述如图8所示。

更新单块FPGA程序时,以一实际测试的3.47 MB大小的配置文件为例,经FPGA在线更新程序固化的时间和使用ISE14.7软件JTAG方式固化的时间如表1所示。

Flash芯片手册中给出的典型擦除和写缓冲时间分别0.5 s和480 μs,则可计算出理论上3.47 MB大小的文件固化所需的典型时间约为41 s。由于器件等因素影响,实测时用时往往大于该时间,但总体来说,使用在线更新方式的耗时要比用JTAG方式耗时更少。

而当更新系统中的10块FPGA时,由于每块FPGA均可同时进行在线更新操作,程序固化所消耗的时间与单块FPGA程序更新时间开销大致相当,可见并行在线更新方式相较于传统JTAG方式无疑可以大大缩短时间。

4 配置文件不断电加载和备份方法

每次更新完配置之后,通常做法是对FPGA进行断电重启实现重新加载,但工程应用时断电可能会影响系统其他模块的正常工作。为使FPGA在不断电的情况下自动加载更新完的配置程序,可通过配置FPGA芯片的PROGRAM_B信号来实现,BPI模式下的时序如图9所示。

考虑到若在配置过程中FPGA发生断电等异常,则Flash中的配置文件损坏,FPGA将无法实现加载,需要重新使用JTAG方式烧写配置文件。为防止该种情况发生,可分配Flash的一块区域用于备份配置文件,发生FPGA无法正常加载的异常时,可读取该备份配置文件实现FPGA再次正常加载,但前提是该部分Flash存储空间预先固化了带有FPGA在线更新功能的程序。

5 结论

本文利用FPGA逻辑设计了一款Flash控制器,实现了FPGA在线更新功能,由于FPGA直接操作Flash,因此相比传统FPGA程序更新方法具有更新速度快、硬件电路精简、易于系统集成等优点,同时能够实现复杂系统多块FPGA并行更新程序,大大节省了程序固化时间,便于项目前期开发及后期排故调试。

参考文献

[1] Xilinx UG360,Virtex-6 FPGA configuration user guide[EB/OL].[2015-11-18].http://www.xilinx.com.

[2] Spansion.S29GL-P MirrorBit Flash family datasheet[EB/OL].[2009-11-20].http://www.spansion.com.

[3] 于乐,王嘉良.易于移植的FPGA在线更新控制器设计[J].航空电子技术,2015(4):47-50.

[4] 杨鹏.基于Linux系统的FPGA芯片在线加载的设计和实现[J].电子设计工程,2015(6):161-164.

作者信息:

林天静,阮 翔,刘 春

(中国电子科技集团第52研究所,浙江 杭州310000)

FPGA配置外围电路设计冲突与解决方法

如前所述,FPGA是由存放在片内的RAM来设置其工作状态的,因此工作时需要对片内RAM进行编程。用户可根据不同的配置模式,采用不同的编程方式。Xilinx FPGA的常用配置模式有主串模式、从串模式、Select MAP模式等。

FPGA和CPLD不同,上电后不能直接工作,而是需要一个配置过程。Xilinx FPGA需要经过8个步骤才能正常地运行用户逻辑,整个流程如图1-8所示。

图1-8 FPGA上电配置步骤

1.FPGA上电启动

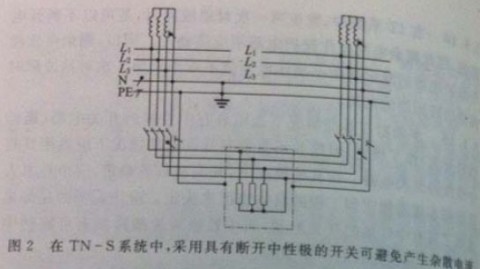

FPGA工作的第一步就是给器件加电。Xilinx要求VCCINT(核心电压)先动,然后再是VCCO(I/O电压),最坏情况是它们之间不能相差1 s以上。在并行配置模式下,要求VCCO_2参考电压必须和FLASH参考电压相同。

在系统正常上电或者PROG-B是一个低脉冲时,FPGA开始配置寄存器空间。这段时间除定义好的配置引脚外,其他I/O引脚均被设置为高阻态(High-Z)。经多次测试,这个阶段需要30 ms左右的时间。

FPGA启动阶段最后一步就是配置启动模式。在PROG-B变高时,FPGA开始采集配置方式引脚(M3、M2、M1),并同时驱动CCLK输出。在这个阶段,有两种方法可以延迟FPGA的配置时序,一种是拉低INIT-B引脚,这是由于FPGA检测到自身还没有初始化完毕,不会进行接下来的操作步骤,这种状态一直保持到INIT-B引脚变高。另一种就是拉低PROG-B引脚,使FPGA处于等待配置状态。

2.FPGA数据加载

FPGA正常数据加载前,需要做一个器件与FLASH之间的同步检查。其方法是传输一个特殊的32位数值(0xAA995566)到FPGA中,提示FPGA下面开始传输的是配置数据。这个步骤对用户来说是透明的,因为Xilinx ISE Bitstream Generator生成的.bit文件中已经自动加入了这个校验码。

在完成配置前的通信同步后,FPGA与FLASH之间还无法识别对方是什么器件,于是Xilinx就给每一个型号的FPGA设计了一个唯一的器件ID号,这个ID号可以在Xilinx配置手册中查到。如XC4VSX35,其ID号为0x02088093。FPGA需要从FLASH中读出这个器件号和自身比对,如果相同就继续下面的步骤,如果不同则配置失败,并打印出配置故障信息。

所有准备工作正常完成后,FPGA开始载入配置文件。这一步对大多数用户也是透明的,由器件自行完成。这也是配置过程中最耗时的步骤,时间从100 ms到几秒不等。在这个过程中,FPGA的所有可配置I/O根据HSWAPEN引脚的设置变为弱上拉(HSWAPE=1)或者高阻态(HSWAPE=0)。这个阶段的I/O引脚还没有变为用户需要的状态,也最有可能影响到其他外围电路的上电时序和运行。设计硬件电路时要特别注意并采取必要措施,如加入上下拉电阻或改变器件加电顺序来尽量避免或减少FPGA配置时对电路其他器件的影响。

配置文件载入完成后,为了验证数据的正确性,FPGA还自动设置了CRC校验(这个在ISE配置选项中也可以去掉,但是为了保证载入数据的正确性,这个是必须选择的)。如果CRC校验不正确,FPGA会自动把INIT-B拉低,放弃这次配置。用户必须把PROG-B引脚拉低,才能进行重新配置。

3.启动序列

CRC校验正确后,FPGA不会马上执行用户的逻辑,它还要进行一些自身内部电路的配置,如DCM锁定(DCMs to Lock)、全局写信号使能(Global Write Enable)等,这些信号的启动顺序也是在ISE配置选项中设置的。必须启动的序列为:释放DONE引脚;释放GTS信号,激活IO引脚;设置全局读/写使能、使能内部RAM和FIFOAssert,结束上电配置。

从上面论述可知,整个FPGA的上电配置正常时序如图1-9所示。

4.FPGA配置外围电路设计冲突与解决方法

FPGA上电配置整个过程大约需要200 ms~2 s,这段时间绝大多数其他外围电路器件都已经上电并正常工作了,而FPGA的通用I/O引脚还处于弱上拉(HSWAPEN=0)或者不定态(HSWAPEN=1),设计时就需要考虑这些器件上电初始化和FPGA通用I/O引脚有无时序冲突。例如,上电时,外围器件要求I/O引脚都为低电平,而FPGA默认是弱上拉,初始化电平产生了冲突;外围器件要求在上电复位后马上采集配置引脚进行初始化,而FPGA还处在配置状态,无法正确上拉或下拉I/O引脚,器件初始化错误;外围器件要求上电初始化前需要时钟锁相,FPGA配置时产生不了时钟,导致器件初始化失败等。解决这些冲突大致有3种方法,但前提都是要正确配置HSWAPEN引脚,这是因为在FPGA执行“器件上电”步骤后(5~30 ms内),它输出的I/O引脚状态是可以通过HSWAPEN设定的。

图1-9 FPGA上电配置时序

方法1:在FPGA的I/O引脚外加上下拉电阻,阻值在1~10KΩ之间,根据实际需要确定。FPGA在上电后10 ms内能通过上下拉电阻把I/O引脚拉到用户需要的电平上,这样能满足上电较慢但是又要求固定电平的外围电路的要求,如功放发射开关和保护开关等。

方法2:FPGA可以在配置完成后产生一个全局复位信号,使外围电路硬件复位,再进行一次初始化操作。这样能解决PowrerPC、ARM这种上电初始化很快(在100ms内就能完成)、但由于FPGA没有配置完成而导致PowrerPC初始化错误的问题。而且这种方式不用外接多余的上下拉电阻,减少了电路设计复杂性。

方法3:FPGA可以在配置完成后产生一个Power Good信号,系统根据此标志再给外围其他有时序要求的器件上电,这样能满足DSP或者高速AD这种需要时钟锁定后再进行初始化的器件的要求。

这3种方法也可根据具体情况混合使用,能达到更好的效果。

5.结论

通过上述分析可知,FPGA上电是一个短暂而复杂的过程,设计时需要充分考虑FPGA上电配置时序和该过程中I/O引脚的各种状态对外围电路的影响。根据系统设计的具体情况,通过选用最合理的配置方式以及外围电路连接,达到了既不影响其他器件性能和整个系统功能,又简化和改善了整个电路设计的效果。

相关问答

Flash 是怎么与 FPGA 连接实现将C程序写入Flash中并从Flash中引导?没听说FPGA可以从flash引导启动。目前的FPGA都是配置EEPROM芯片,如果要使用C语言,必须有相应的转换系统,譬如altera公司的NIOS就可以实现C语言编程下载到FPGA...

研究生学习集成电路( FPGA 方向)前景如何?推荐哪些公司?可以说,FPGA芯片是小批量系统提高系统集成度、可靠性的最佳选择之一。FPGA可做其它全定制或半定制ASIC电路的中试样片。采用FPGA设计ASIC电路(专用集成电路),...

FPGA 开发板里面的程序如何导出?FPGA旁边的FLASH存储器中存放的是FPGA的配置数据,而不是硬件描述语言源代码。即使你将这些配置数据导出,也无法查看原始设计是怎样的。FPGA旁边的FLASH存储器...

一块开发板上的多个 FPGA 间如何通讯?对于多个FPGA之间的通信,只要IO连接上了,对于高速的数据流需要同步时钟,对于低速的接口,只需要异步处理即可。下面介绍几种FPGA之间常用的数据通信方式。一...4...

fpga 基于什么可编程结构?尽管FPGA和CPLD都是可编程ASIC器件,有很多共同特点,但由于CPLD和FPGA结构上的差异,具有各自的特点:①CPLD更适合完成各种算法和组合逻辑,FPGA更适合于完成时...

卡脖子概念股龙头有哪些?-股票知识问答-我爱卡[回答]ST乐凯:中国航天科技集团旗下,生产的压力测试膜是京东方、深天马除日本富士外国内唯一的供应商;EMI屏蔽膜和导电胶膜成为5G产品发力点是国内除方邦...

XC5VLX50TFPGA的配置 flash 能用XCF32P的吗?5VLX50T是容量很小的FPGA,不需要XCF32P那么大容量。你在数据手册里查下50T的配置数据多大,比如10M,那就选XCF16,16M的flash。XCF32是32M的flash。可以用的,...

emif总线详解?EMIFC6455的EMIF模块EMIF是ExternalMemoryInterface的简称。个人认为它是DSP比较强大的地方之一。通过EMIF接口,使得DSP可以和F...

从altera转xilinx容易吗?从altera转xilinx容易。Xilinx把基于查找表、SRAM工艺、要求外挂配置用EEPROM的PLD叫FPGA,把基于乘积相、FLASH(类EEPROM)工艺的PLD叫CPLD。Alter...

CPLD支持什么在线调试工具?1.1.SJ-8002B电子测量实验箱1台2.计算机(具有运行windows2000和图形化控件的能力1台3.函数发生器1台4.SJ-7002CPLD实验板1块5.短接线若干...