UFS深入浅出 第二章 UFS结构 第四节 UFS分块图解

Section 4 UFS block diagram

第四节 UFS分块图解

In this section, we will have a high-level view of UFS block diagram. Meanwhile we will also have a data flow overview in-between each block. Detail of each block will be covered in the following chapter.

在这一节里,我们会比较笼统的看一下UFS的分块图解。同时,我们也会看一些各个块之间的数据流动。每个块的具体细节会在接下来的章节里面涵盖。

On left of the diagram is Host, is composed by SoC, RAM and UFS Host Controller. The Host here does not simply mean UFS host, but the host of the whole system. While the UFS device is on the right side, which contains UFS Device Controller with embedded SRAM and standalone NAND Flash media.

在分解图的左边是Host,由SoC,RAM和UFS 主机控制器组成。这里的主机不是简单的指UFS 主机,而是整个系统的主机。UFS器件则在右边,包括了UFS 器件控制器以及内嵌的SRAM和独立的NAND Flash 闪存。

If you look into detail of UFS Host Controller and UFS Device Controller, you will find they are quite similar like each other with the same internal layer structures. The difference is that there is a UFS Host Controller Interface called UFS HCI in Host Diagram to communicate with Host SoC, while UFS device controller has got a NAND interface to connect with NAND in which Logic Unit and Registers physically reside. The same part in both sides is defined in the JEDEC UFS specification (latest one is JESD220F UFS4.0). JEDEC also has a HCI Specification (latest one is JESD223E UFSHCI4.0) for UFS Host Controller Interface. Regarding NAND interface, JEDEC absorbs ONFI (Open NAND Flash Interface), and this part will be covered in the article NAND Step by Step.

如果你仔细看UFS 主机控制器和UFS 器件控制器,你会发现他们彼此非常相像,都有着一样的内部层结构。不同的地方是UFS 主机控制器里面有一个叫做UFS HCI的UFS 主机控制器接口与主机SoC通讯。而UFS 器件控制器则有一个NAND接口与保存逻辑单元和寄存器的NAND 闪存通讯。两边相同的地方是在JEDEC UFS规范(最新的是JESD220F UFS4.0)。JEDEC还有一个给UFS 主机控制器接口的HCI规范(最新的是JESD3F UFSHCI4.0)

Usually in a traditional small system, there will be a CPU, RAM, and Disk. When we take a full picture of this diagram, the SoC (System on Chip) here acts as CPU in embedded system, RAM here refers volatile Dynamic RAM memory normally,either DDR RAM or LPDDR (Low Power DDR) RAM,for high-speed code or data access. Disk here is our leading role UFS device, which is a non-volatile memory to store the code and data without power supply. Please take a note that, Disk here is not an accurate name. Disk originally refers to Hard Disk Drive (aka HDD) which uses magnetic material for data non-volatile storage. Now we use this terminology simply for all non-volatile memory for easy understanding.

通常在一个传统的小型系统里面会有CPU,RAM和Disk。当我们整体来看分解图的时候,SoC(片上系统)在嵌入式系统里面扮演了CPU的角色。RAM这里通常是指易失的动态RAM存储器,可以是DDD RAM或者是LPDDR(低功耗DDR)RAM,主要是为了高速代码或者数据的访问。这里的Disk是我们的主角UFS器件,不需要电的非易失存储器。请注意这里的Disk不是一个准确的名字。Disk原本指的是为了数据的非易失存储而使用磁存储介质的硬盘驱动器(也叫HDD)。为了便于理解,现在我们用这个术语简单指代所有非易失存储器。

If we zoom in to focus only on UFS device side, the internal SoC (Yes, there is one SoC inside UFS device controller as well, invisible in this Diagram)of UFS Device controller will be CPU, controller internal SRAM will act as volatile RAM, and NAND flash is non-volatile Disk. Since in this article, we illustrate UFS protocol only, hence we will not go deeper into UFS device small system.

如果我们放大聚焦在UFS器件这边,UFS器件控制器里面的 SoC (是的,在UFS器件控制器里面也有SoC,这个图解里面不可见) 是CPU,控制器内嵌的SRAM是易失的RAM,而NAND闪存就是非易失的Disk。因为这篇文章我们只解释UFS协议,所以我们不会深入探究UFS器件的小系统。

Back to the small system SoC, DRAM, UFS, the main function of Flash is to store data since it is non-volatile memory and could keep data inside without power supply. But in order to load and save data into the NAND Flash, Host SoC need go all the way down through each layer of the UFS host Controller to the physical signals and goes up back through the correlative layers of UFS Device Controller to communicate with NAND Flash. This is the way that we use NAND Flash to save data, the opposite direction is load data.

回到SoC,DRAM和UFS的小系统,Flash的主要功能是存储数据,因为它是非易失存储器,可以在没有电供应的情况下保持数据。但是为了提取和保存数据,主机SoC需要一路向下穿过UFS主机控制器的每一层直到物理信号,然后再往上穿过相对应的UFS器件控制器的每一层去和NAND闪存通讯。这个是我们用NAND闪存存数数据的方式,相反的方向则是提取数据的方向。

We could also use dot line with arrow to see how they communicate with each other logically. On the top is the pair of Host SoC and NAND Flash for read and write operation. In the very beginning, Host SoC do access NAND Flash directly, but limitation is quite obvious. NAND 8-bit parallel I/O is not good to increase data rate for long distance transmission. NAND is born with bit errors for cost effective higher density, hence ECC (Error Correction Code), BBM (Bad Block Management) which bring extra burden for SoC. It does not count WL(wear-leveling)for overcoming limited NAND Flash P/E(Program/Erase) characteristic and FTL (File Transfer Layer) of easily use NAND Flash which need be access by pages but not bit. This is the reason why NAND controller and complex protocol needed for higher and higher data rate.

我们还可以给每一层用虚线箭头来展示逻辑上它们是怎么互相联系的。在最上面是读写操作的一对,主机SoC和NAND闪存。在最开始,主机SoC确实是直接访问NAND的,但是局限性也非常明显。NAND的8比特并行I/O不利于在长距离传输提高数据传输率。NAND天生就是为了更高容量节省成本而有比特错误,所以ECC(错误纠正码),BBM(坏块管理)会给SoC额外的负担。这个还没算为了克服有限的NAND闪存的P/E(编程/擦除)特性而使用的WL (磨损均衡),以及为了方便管理NAND闪存这种使用页而不是比特访问而使用的FTL(文件转换层)。这个也是为了越来越高的速度需要使用NAND控制器以及复杂的协议的原因。

UCS (UFS Command Set) block use CDB (Command Descriptor block) for communication. CDB is defined by SCSI specification which implement not only read/write command but also other functional commands.

UCS(UFS指令集)模块用CDB(命令描述符块)来做通讯。CDB是SCSI协议定义的用来实现读写命令以及其它功能命令。

These commands CDB are embedded in in the next lower UTP (UFS transport Protocol) layer‘s UPIU (UFS Protocol Information Unit) Frame. Besides the communication to the peer layer, UPIU is also used internally by Task Manager block and Device Manager block.

这些命令CDB会嵌入到下面低一层的UTP(UFS传输层)的UPIU(UFS协议信息单元)帧里面。除了用于与对面对应层的通讯,UPIU也被用于内部的任务管理块和器件管理块。

Go deeper to UIC (UFS InterConnect) layer, UniPro is a software stack to hand so called credit-based flow control data transmission. PDU (Protocol data Unit) is the common name for the data packet in UniPro, each sub layer has its specific PDU name. UPIU from upper UTP layer will be divided here to fit for the PDU format. Device Manger block could skip UTP layer to access directly the DME (Device Manager Entity) in UniPro. This is like the internal employee private path for better control low level configuration.

在深一点去到UIC层, UniPro是一个软件协议栈用于处理被称为基于信用的流控数据传输。PDU (协议数据单元) 是UniPro里数据包的通用名字,每一个子层都有各自的专用PDU命名。从上面UTP层来的包在这里会被拆分来适配PDU格式。器件管理块能够越过UTP层直接访问UniPro里的DME(器件管理实体)。这个就像是内部员工的私人通道来更好地控制底层配置。

M-PHY in the UIC will finally encoded sending data or decoded receiving data into symbols and turn it to or from physical signals in the lane. M-PHY use 8b/10 line encoding to turns 8bit data into 10bit symbol for both High-Speed and Low-Speed. Regarding binary encoding,M-PHY for UFS use PWM (Pulse Width Modulation) for low Speed, while NRZ (Non Returned to Zero) for High Speed.

UIC里的M-PHY最终会把发送数据编码或者把接收数据编码成字符,然后转化成通道上的物理信号。高速或者低速M-PHY都使用8b/10b的线路编码把8比特字节转换成10比特的字符。而二进制编码,UFS的M-PHY的低速使用PWM(脉宽调制),高速则使用NRZ(非归零)。

The access point of in-between each diagram block is called SAP (Service Access Point), this could be thought of as logical API (Application Programming Interface).

在各个块之间的访问点被叫做SAP(服务访问点),这个可以被想象成为逻辑API(应用编程接口)。

SoC will utilize the system RAM to maintain the Task Manager request list and Command Transfer request list. These will notify UFS host controller for dispatching instructions by doorbell register which reside in UFS HCI. The name doorbell is quite vivid as if someone is knocking your door to tell you, hey, the tasks and commands are waiting for you to execute them. UFS device controller also maintains the task and command queue in its internal SRAM which is not defined in UFS specification and should be implemented by UFS device vendors.

SoC会使用系统RAM来维护任务管理请求列表和命令传输请求列表。这个会通过UFS HCI里面的门铃寄存器来通知UFS主机控制器分发指令。门铃寄存器这个名字非常生动,好像是有人正在敲门告诉你,嘿,任务和命令已经准备好等你执行了。UFS器件控制器同样在它内部的SRAM维护了任务和命令队列,这个在UFS规范里面没有定义,需要UFS器件厂家自己实现。

存算一体:NOR Flash冲向新巅峰

近年来,在算力急速增长的推动下,以神经网络为代表的人工智能迎来了新一轮的发展,并迅速在图像视频应用、自然语言处理及其他诸多领域取得了惊人的成就。尤其是边缘计算在终端设备推理的兴起为人工智能提供了大量的计算设备和数据,使得人工智能具有了无限的可能。但是,神经网络对于庞大算力的需求和边缘及终端侧对于低功耗的需求之间难以调和的矛盾,严重阻碍了神经网络的进一步发展和应用,因此低功耗、高能效神经网络加速器成为了众多企业、研究机构的研究重点。

在这样的基础上,存算一体孕育而生。

为什么需要存算一体?

2018 年,美国DARPA“电子复兴计划”明确提出不再依赖摩尔定律的等比例微缩道路,旨在寻求超越传统冯·诺依曼计算架构的创新,利用新材料、新器件特性和集成技术,减少数据处理电路中移动数据的需求,研究新的计算拓扑架构用于数据存储与处理,带来计算性能的显著提高。

与传统的计算单元和存储单元分离的冯诺依曼架构不同,存算一体技术可以把存储单元同时用于计算和存储,这样就可以避免数据和计算结果在计算单元和存储单元之间来回搬运引起的功耗和带宽瓶颈,从而实现功耗的大大降低。

基于NOR Flash的存算一体

而基于 NOR Flash 的存算一体方案正是受到多方关注的一条技术路线。英特尔、博世、美光、Lam Research、应用材料、微软、亚马逊、软银都投资了基于NOR Flash的存内计算芯片。

NOR Flash的起源和技术发展

Nor是Flash一种架构方式。Flash存储技术是在它之前的E2PROM (Electrically Erasable Programmable Read OnlyMemory)基础上发展起来的存储器,它跟E2PROM一样,也是使用电学方法来存储电荷的器件,只是E2PROM是使用两个晶体管来构成,而Flash存储阵列中的存储单元是由一个晶体管组成的。所以Flash存储器在器件集成度、数据容量和功耗低等性能上都比之前的器件有明显的提高。

目前性价比最高的存储器首推闪存,闪存主要有NOR和NAND两种类型。NOR Flash 由英特尔公司于1988年最初推出。为了提高容量/价格比,东芝公司于1989年推出NAND Flash。但相比NOR Flash来说,两种Flash技术各有优、缺点以及各自适用的场合。NOR结构的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在Flash闪存内运行,不必再把代码读到系统RAM中,节省了时间。NAND结构的特点能提供极高的单元密度,可以达到高存储密度,并且增加写入和擦除的速度。

NOR Flash的原理

浮栅晶体管的横截面

NOR Flash的存储单元是浮栅晶体管,在作为存储使用的时候每个浮栅晶体管可以存储1bit数据。它是在金属-氧化物半导体场效应晶体管(MOSFET)的基础上引入浮置栅极来存储电荷而实现的。一个浮栅晶体管,由P型的衬底和在其上重掺杂的N型源极和漏极、控制栅极、由氧化物包围的多晶硅浮栅组成。浮栅是由绝缘介质层包裹起来的,浮栅和沟道之间的很薄的氧化物层被称为隧道氧化层,两个多晶硅栅之间的氧化物层被称为栅氧化层,一般是氧化物-氮化物-氧化物层组成的多晶桂层间绝缘介质。因此,其上的电荷会轻易地流失,因而浮栅晶体管能够应用于NVM。

浮栅和控制栅可以用来控制源极和漏极之间沟道的形成:当浮栅处于无电荷状态时,浮栅晶体管会如MOSFET—样,当控制栅加高于阈值电压(Threshold Voltage)的电压时,沟道形成,浮栅晶体管处于导通状态,而控制栅上加的电压低于阈值电压时,浮栅晶体管处于截止状态;当浮栅上存储一定量的电子后,由于浮栅的影响,会升高,浮栅晶体管更加难以导通。这样,就可以通过这两种状态来存储数据,分别表示“1”和“0”,并且可以通过在栅极上加一个在两种之间的电压,根据流过的电流来读取存储在浮栅晶体管中的状态。

浮栅上的电子则可以使用沟道热电子注入(Channek Hot Electronic Injection, CHEI)FN隧穿(Fowler-NORdheim Tunneling)两种方式来增加和移除。CHEI通过在栅极加电压使得沟道反型,并在源极和漏极之间加高电压使电子向漏极加速。其中有部分电子在整个过程中侥幸因为发生碰撞而获得了足够越过隧道氧化层势垒的动能并到达浮栅,这样,就使得浮栅中有了多余的电子。而FN隧穿则在控制栅和衬底之间加很高的负电压,使得它们之间形成强电场以降低氧化层的势垒宽度,增加电子隧穿的几率,使得电子从浮栅回到衬底。使用CHEI增加浮栅电子的操作称为“编程”,而使用FN隧穿移除电子的操作称为“擦除”。

可见,浮栅晶体管可以近似等效于一个N沟道MOSFET在栅极连接一个电容,其电学特性就像阈值电压可调的MOSFET,也具有截止(Cut-Off)、 弱反型( Weak-Inversion,亦称Sub-threshold,亚阈值)、线性(Linear, 亦称Triode,三极管,亦称Ohmic,可变电阻)和饱和等工作模式,每种模式具有不同的特征。

NOR Flash阵列结构

NOR Flash中程序和数据可存放在同一芯片上,拥有独立的数据总线和地址总线,能够快速随机读取数据,也允许系统直接从Flash中读取代码执行,而不需要先将代码下载至RAM中再执行;可以单字节或单字编程,但不能单字节擦除,必须以块为单位或对整片执行擦除操作,在对存储器进行重新编程之前需要对块或整片进行预编程和。

NOR Flash 以并行的方式连接存储单元,具有分离的控制线、地址线和数据线、较快的读速度、能够提供片上执行的功能,但写操作和擦除操作的时间较长,且容量低、价格高。因此NOR Flash 多被用于手机、BIOS 芯片以及嵌入式系统中进行代码存储。

NOR Flash如何实现存算一体?

基于NOR Flash的存算一体基本原理是利用存储单元的多值特性,通过器件本征的物理电气行为(例如基尔霍夫定律与欧姆定律)来实现多值MAC 运算。每个存储单元可以看作一个可变电导/电阻,用来存储网络权重,当在每一行施加电流/电压(激励)时,每一列即可得到MAC 运算的电压/电流值。

基于Flash的MAC运算基本原理

我们以基于Flash单元的电压式模拟乘法器为例。模拟乘法器由两个Flash单元构成,这两个Flash管栅极(G)相连并接固定电压,漏极(D)相连接电压VDS,源极(S)的电流相减为输出电流ID。外部输入数据X经过DAC(Digital to Analog Converter,数模转换器)转换为模拟电压VDS,得到的输出电流经过ADC (Analog to Digital Converter,模数转换器)转换为数字信号输出。可以使用两个工作在线性区的Flash管实现模拟乘法。

电压式模拟乘法器结构图

NOR Flash相比其他存算结构的优势

Flash器件于1967年被施敏发明,在MOS管的栅极增加一个浮栅,通过改变浮栅中的电荷达到存储数据的目的。经过50多年的发展,浮栅器件的制造工艺已经非常成熟,成品质量稳定。浮栅单元具有密度大,效率高的特点,适合作为实现存算一体架构的介质。

存算结构特点对比

相比其他存算结构,NOR Flash有两大突出优势。

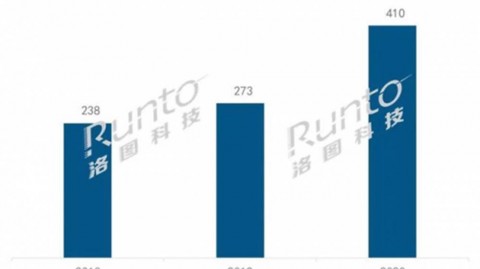

其一,因为其长期的应用和发展,闪存技术已经非常成熟,NOR Flash 已被大量应用于手机、BIOS 芯片以及嵌入式系统中进行代码存储。 美光(Micron) NOR Flash 产品线总监 Richard De Caro 曾表示,在传统的精密电子产 品的生产中,NORFlash的作用举足轻重,涵盖了各个细分市场。根据 Richard De Caro 的估算,每年 NOR Flash 的出货量超过 60 亿颗。NOR Flash成本低于其他存算结构,技术成熟,已有量产芯片出现在市场。

其二,NOR Flash属于非易失性存储器,可以直接存储网络权重,因此不需要片外存储器,减小芯片成本。 例如Mythic的产品 MP10304 PCIe并不需要额外的片外存储;同时,非易失性可以保证数据掉电不丢失,从而实现即时开机/关机操作,减小静态功耗,延长待机时间,非常适用于功耗受限的边缘终端设备,例如国内企业知存科技量产的芯片WTM2101专注于可穿戴设备,和现有芯片在AI算力上有数十倍到百倍的提升。

NOR Flash学术研究及产业应用进展

在学术方面,国内外高校都有研究。美国加州大学圣塔芭芭拉分校的研究团队通过修改NOR Flash阵列结构实现了对单个Flashcell的编程擦除操作,并在此基础上构建了一个包含两层全连接层的神经网络,该计算阵列识别一张图片能耗低于20nJ。并且该团队还进一步设计了计算精度为5Bit,大小为400X400的由Flash构成的乘累加单元。北京大学的研究团队提出了针对大尺寸图像卷积的分块计算方式,实现了对大尺寸图像的二维卷积操作。

在产业方面,国内外企业中基于NOR Flash的存算一体都正飞速发展,且有量产芯片出现在市场。目前存算一体技术处于多种存储介质百花齐放的格局,如Flash、SRAM、MRAM等等。如今选择SRAM介质阵营的主要有苹芯科技、后摩智能、九天睿芯;MRAM方面,三星电子于2022完成世界上第一个基于 MRAM的内存计算流片,并发表在《nature》,而Flash阵营的代表玩家则有美国的Mythic,与国内知存科技、合肥恒烁。

国外相关领域的佼佼者是美国公司Mythic,该公司于2012年成立,专注于研发深度学习的神经网络芯片的公司,其推出的新型的芯片和软件,无需通过云端就能在本地设备中实现语音控制、计算机视觉和其他的AI技术。在2019年推出基于Flash 的神经网络处理单元IPU。IPU的性能达到4TPOS/W。Mythic于2020 年 11 月推出业界首款模拟矩阵处理器 (Mythic AMP™)。并于2021年推出 MP10304 PCIe 卡,该卡具有四个 M1076 Mythic 模拟矩阵处理器 (AMP),提供高达 100 TOP 的 AI 性能,且不需要片外存储器,减小芯片成本,并在不到 25W 的功率下支持多达 3.2 亿个权重,用于复杂的 AI 工作负载。Mythic着重在较小的功耗下实现高性能的神经计算。

Mythic MP10304 Quad-Amp PCIE卡

国内企业也在发力基于NOR Flash的存算一体。其中的领先者是知存科技。知存科技公司与科大讯飞合作,于2016年发布了基于Flash的MemCore001芯片,支持智能语言识别、语音降噪等多种智能语音应用。2018年,知存科技即针对智能语音应用场景设计了国际领先的高精度、低功耗Flash存算一体芯片架构,并首次应用MemCore001/MemCore001P系列芯片。并于2022年3月宣布其WTM2101芯片正式量产并推向市场, WTM2101的AI算力高达50Gops,相较于可穿戴设备现有芯片在AI算力上有数十倍到百倍的提升。

知存科技的存算一体模块基于高密度非易失性存储器,8-bit量化的深度学习算法参数量支持高达1.8M个,可同时运行2-3个高性能模型。知存科技着重在可穿戴设备方向,且已于今年实现量产芯片。

知存科技 WTM2101

国内的另一家企业是来自合肥的恒烁半导体科技公司,其于2019 年底宣布公司第一款CiNOR V1版在武汉新芯65nm NOR Flash制程上已经完成芯片设计并流片,成功验证了CiNOR芯片原理和可行性,并实现了包括手写识别、ECG检测和人脸检测等几项应用。

基于 NOR Flash 的存算一体芯片避免了传统 AI 架构芯片碰到的“存储墙”和“功率墙”瓶颈,显著提高了运算效率,并且大幅降低功耗,同时 NOR Flash 带来制造成本上的竞争优势,成本低于其他存算结构,技术成熟,已有量产芯片出现在市场,且Flash属于非易失性存储器,可以直接存储网络权重,因此不需要片外存储器,减小芯片成本。我们相信该类芯片会有更好的未来。

相关问答

塔影城上的影片如何下载D如何下载在线电影!(一些下载电影的小技巧)(一)观看电影软件及技巧一般都用realplay及WindowsMediaPlayer。在线观看的电影一般有几种格式,如...

怎么在压缩文件里加入一个网址超链接文件?-ZOL问答1、首先确认电脑上安装有压缩、解压缩软件,如winrar、好压等2、右击选中楼主需要操作的压缩文件,点击“打开”,将采用默认的压缩文件程序打开,在弹出的界面中...

网页头信息的构成?HTTP网页头部信息构成解释分析(详细整理)HTTP头部解释1.Accept:告诉WEB服务器自己接受什么介质类型,*/*表示任何类型,type/*表示该类型下的所有子类型,...

内存卡是怎么储存东西的? - 黄大大大大奕 的回答 - 懂得其基本单元电路(存储细胞)如下图所示,常采用浮空栅雪崩注入式MOS电路,简称为FAMOS。它与MOS电路相似,是在N型基片上生长出两个高浓度的P型区,通过欧...

求推荐支持VR渲染器的渲染平台?模型太大了,自己的电脑带不动...无法使用超过4G内存,所以必须给系统留出缓存,安全范围内应用程序最多只能分配3G)具体修改方法如下xp系统看这篇:http://archive.hxsd/sho...t=9644...