ADALM2000实验:TTL逆变器和NAND门

自20世纪60年代首次生产出集成逻辑门以来,各种数字逻辑电路技术层出不穷。本次实验将研究晶体管-晶体管逻辑(TTL)电路逆变器(非门)和2输入NAND门配置。

背景知识

TTL逆变器的原理图如图1所示。此电路克服了单晶体管逆变器电路的局限性。基本TTL逆变器由三级组成:电流导引输入、分相级和输出驱动级。

图1. TTL逆变器

输入级晶体管Q1执行电流导引功能,可以将它视为背靠背二极管布置。晶体管以正向或反向模式工作,使电流流入或流出第二级晶体管的基极Q2。正向电流增益ßF远大于反向电流增益ßR。关断时,它提供更高的放电电流来给基极放电。

图2. 输入电流导引级的等效电路

图1中的第二级晶体管Q2使用分相器来驱动上拉和下拉输出级的两半。它允许以相反相位产生输入条件,从而可以反相驱动输出晶体管。这样,Q4关断时Q3可以导通,反之亦然,

创意路上不孤单,唯样商城,从创意到产品一路相伴

如图3所示。

图3. 分相级

输出晶体管对Q3和Q4与二极管D1一起被称为图腾柱输出,如图4所示。这种输出配置提供了主动拉电流或灌电流的能力,对于驱动容性负载很有用。电阻R4用于限制VCC提供的电流。在稳态条件下,一次只有一个晶体管导通。

图4. 输出级

二极管D1用于提高Q4的有效导通电压,使其能够在Q3完全导通之前关断。这有助于防止逻辑状态转换期间潜在的大浪涌电流流入输出级。电阻R4还用于限制输出级中允许流动的电流。缺点是逻辑高电平会降低,降幅为二极管压降,如图11所示。

材料

● ADALM2000 主动学习模块

● 无焊试验板

● 跳线

● 一个100 kΩ电阻

● 一个2.2 kΩ电阻

● 一个470 Ω电阻

● 一个100 Ω电阻

● 一个小信号二极管(1N914)

● 五个小信号NPN晶体管(2N3904和/或SSM2212)

TTL逆变器

说明

ADALP2000 模拟部件套件随附五个2N3904 NPN晶体管。较旧的套件可能包含一对匹配的SSM2212。所示的建议试验板布局是针对SSM2212连接。如果只使用2N3904器件,请根据需要更改布局。

在无焊试验板上构建图5所示TTL逆变器电路。如果使用SSM2212 NPN对,它只能替代Q3和Q4(输出级),因为其基极和发射极端子上有内部保护二极管用以防止反向偏置。

图5. TTL逆变器

硬件设置

将电路连接到ADALM2000输入/输出连接器,如图5所示。对于未使用的示波器负输入,在不使用时最好将其接地。

试验板连接如图6所示。

图6. TTL逆变器试验板电路

程序步骤

将波形发生器W1配置为具有0 V偏移和6 V幅度峰峰值的100 Hz三角波。在x-y模式下使用示波器观察电路的电压传输曲线。

图7. TTL逆变器传输曲线

TTL NAND门

说明

给TTL逆变器再增加一个输入,便得到一个TTL NAND门。按照图8所示连接TTL逆变器电路。

图8. TTL 2输入NAND门

硬件设置

将电路连接到ADALM2000 I/O连接器,如图8所示。对于未使用的示波器负输入,在不使用时最好将其接地。

试验板连接如图9所示。

图9. TTL 2输入NAND门试验板电路

程序步骤

将波形发生器W1配置为具有0 V偏移和6 V幅度峰峰值的100 Hz三角波,将W2配置为具有0 V偏移、6 V幅度峰峰值和90°相位的100 Hz三角波。

使用示波器观察电路的输出Ch2。

图10. TTL NAND门输出波形

测量

传输特性

通过施加缓慢上升的输入电压,并确定相对于每个晶体管的导通状态变化而发生的事件序列以及这些变化发生的临界点,可以推导出TTL逆变器的传输特性。考虑图11所示的电路输入与输出传输特性曲线。

图11. TTL逆变器输入与输出传输曲线

断点P1

当输入接近0 V且基极电流提供给Q1时,该晶体管可以在正向模式下导通。集电极电流的唯一来源是Q2的漏电流,因此Q1将被驱动到饱和状态。这确保了Q2关断,进而又意味着Q3关断。在没有负载的情况下,输出级中有漏电流流动,这使得晶体管Q4和二极管D1在导通状态下几乎不传导电流。

断点P2

随着输入电压略微增加,上述状态一直持续,直到(在Q1导通并处于饱和状态的情况下)Q2基极的电压上升至导通点。则

断点P3

随着输入电压进一步增加,Q2传导更多电流,从而完全导通。Q2的基极电流由Q1的基极-集电极结(现在是正向偏置)提供,Q1仍处于饱和状态。最终,Q3达到导通点。这发生在:

请注意,当晶体管Q3刚刚导通时,VBE3 = 0.6 V,这意味着流过R3的电流为0.6 V/470 Ω = 1.27 mA。在线性活动区工作时,Q2的集电极电流为0.97 mA × 1.27 mA = 1.23 mA。

R2两端的电压降即为VR2 = 1.23 mA × 2.2 kΩ = 2.7 V。

在这种情况下,Q2上的集电极到发射极电压降为:

这证实了Q2仍在正向活动模式下运行。

随着Q3开始导通,电流通过Q4和二极管D1的传导路径,随后完全导通。这种情况下:

断点P4

随着输入电压进一步增加,Q2传导更多电流,最终进入饱和模式。Q3也传导更多电流,最终达到饱和点。当Q2传导更多电流时,其集电极电流增加。这导致R1两端的压降增加,意味着Q2上的电压(即VCE2)下降。当此电压降至Q4和二极管D1导通所要求的电压以下时,二者均关断,然后Q3饱和。

当Q3达到饱和边缘时:

问题:

1. 典型TTL逻辑门的输出电路通常被称为图腾柱输出,原因是其两个输出晶体管相互堆叠,就像图腾柱上的雕像一样。具有图腾柱输出级的门电路能否提供负载电流、吸收负载电流或既能提供又能吸收负载电流?

全球首款321层NAND ,发布!

报名提醒

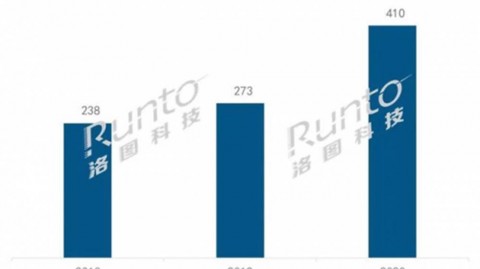

2023 中国汽车半导体新生态论坛 (明天见)在今日于美国举行的 2023 年闪存峰会 (FMS),SK海力士正式公布了公司的 321 层 1Tb TLC 4D NAND 闪存的开发进展,并展示了样品。值得一提的是,这是全球首款突破三百层的存储。

SK海力士发言人表示:“基于成功开发业界最高238层NAND并已量产的经验,我们321层产品的开发进展顺利。” “随着解决堆叠限制的又一次突破,SK海力士将开启300层以上的NAND时代,并引领市场。”

该公司表示,321层产品的生产率比其238层前代产品高出59%,其数据存储单元堆叠得更高,从而提高了单片晶圆的整体容量。随着ChatGPT的爆发式普及,生成式AI市场快速增长,这增加了对能够更快地处理更多数据的高性能、大容量存储芯片的需求。

为了顺应这一趋势,SK海力士还在闪存峰会上推出了针对此类AI需求优化的下一代NAND产品,包括支持PCIe Gen5接口和UFS 4.0的企业级固态硬盘(SSD)。。

该公司预计这些产品将实现行业领先的性能,以充分满足客户以高性能为重点的需求。SK海力士NAND开发主管Choi Jung-dal在主题演讲中表示,该公司预计321层产品的持续开发将有助于巩固其在NAND内存领域的技术领先地位。Choi表示:“随着高性能、大容量NAND的适时推出,我们将努力满足AI时代的要求,并继续引领创新。”

3D NAND,轻松突破300层

关于3D NAND Flash未来的发展,提升密度和增加层数是产业界聚焦的两个方向。而在ISSCC 2023 会议上,韩国存储巨头SK海力士提交了一篇论文,展示了他们如何开发出 300 层以上的 3D NAND 技术,以创纪录的 194GBps 速度摄取数据。

在这篇又35名SK海力士工程师写就的论文里,他们写道:”“NAND 闪存领域最重要的主题是持续改进性能和降低成本/位。为了降低成本/比特,需要增加堆叠层数,同时减小堆叠层之间的间距。有必要管理由减小的堆叠间距产生的增加的 WL(字线)电阻。”

他们将五项新技术应用于 >300 层 1Tb 3b/cell (TLC) 3D-NAND 闪存产品:

1、三重验证程序 (TPGM:triple verify program ) 技术用于提高程序性能;

2、自适应未选择串预充电 (AUSP:adaptive unselected string pre-charge) 技术用于减少干扰和编程时间 (tPROG:reduce disturb and program time);

3、编程虚拟串 (PDS:programmed dummy string ) 技术用于减少 WL 稳定时间;

4、全通上升 (APR:all-pass rising) 技术用于减少读取时间 (tR);

5、在擦除期间使用平面级读取重试 (PLRR:plane-level read retry ) 技术来提高 QoS;

TPGM 方案通过缩小单元阈值电压 (VTH) 分布来降低 tPROG。SK 海力士目前的双重验证程序 (DPGM) 方案将单元分为三组,而 TPGM 将单元分为四组,因此能够更好地管理其编程(写入)性能。该论文称,这“导致大约 10% 的程序时间减少”。

我们被告知,AUSP 技术将编程时间再缩短了 2%。PDS 方案通过减少影响字线建立时间的电容性负载做出贡献。APR 方案将字线的响应时间缩短到一个新的电压电平,并将读取时间缩短 2%。

这些边际和接近边际收益的累积效应是 1 太比特 300+ 层 TLC NAND 单元,具有 20Gb/mm²位密度和创纪录的 194GBps 写入速度,如表所示:

该论文中还包含了 300 层芯片的图像:

我们已将此 SK 海力士 300 层技术添加到我们的表格中,以比较和对比供应商的 3D NAND 技术:

如图所示,SK 海力士(红色椭圆形)显然在 3D NAND 层数方面处于领先地位。据我们估计,该产品可能会在今年晚些时候或 2024 年出现,并且应该能够在更小的物理空间内实现更大容量的 SSD。

以下为SK海力士原文译文:

高性能1Tb 3b/Cell 3D-NAND闪存

在超过300层上具有194MB/s的写入吞吐量

随着多媒体产生的数据爆炸式增长和对数据存储需求的增加,NAND-Flash存储领域最重要的主题是持续的性能改进和成本/比特的降低。为了提高性能,需要提高服务质量(QoS)和读写性能的特性。

为了降低成本/比特,需要增加堆叠层数,同时降低堆叠层之间的间距。有必要管理由于堆栈间距减小而产生的不断增加的WL电阻。为了克服这些挑战,本文介绍了应用于>300层1Tb 3b/cell (TLC) 3D-NAND闪存的技术:1)使用三重验证编程(TPGM)技术来改进编程性能。2)采用自适应非选择串预充电(AUSP)技术减少干扰和编程时间(tPROG)。3)采用编程虚拟串(PDS)技术减少WL建立时间。4)采用全通上升(APR)技术减少读取时间(tR)。5)在擦除过程中采用平面级读取重试(PLRR)技术提高QoS。

TPGM方案通过缩小单元阈值电压(VTH)分布来降低tPROG。增加步进电压(VSTEP)是减少编程时间的一种方法,其中增量步进脉冲编程方法增加了步进电压(VSTEP),但使VTH分布更宽。然而,改善VTH分布对于提高步进电压和缩短编程时间是至关重要的。在编程操作中,阈值电压差(ΔVTH)由施加到WL的阶跃电压和沟道电压(VCH)之间的差值决定。图28.2.1 (a)和图28.2.1 (b)是双验证方案(DPGM)与TPGM方案的区别。

DPGM方案根据编程验证(PV)电平将单元分为三组,然后通过施加三种不同的BL电压(VBL)来控制每组的沟道电压。对组1 (GR1) BLs应用VDD实现信道隔离;GR1的单元没有被编程。VA用于第2组(GR2)BLs, ΔVTH = VSTEP-VA。0V用于第3组(GR3) BL,ΔVTH=VSTEP。在DPGM中,VTH分布可以通过两种ΔVTH进行改进。在DPGM现有的三个组中再增加一个组(ΔVTH=VSTEP-VB,VA>VB)。TPGM根据电池的PV水平将电池分为四组,并通过施加四种不同的BL电压来驱动每组的沟道电压。

图28.2.1(c)给出了防止BL耦合效应的计数器驱动方案。BL1由NMOS串联驱动,设置为VREF1-VTHN,BL2初始设置为VDD,并通过串联连接的PMOS与NMOS放电到VREF2+VTHP。VTHN和VTHP分别为NMOS和PMOS的阈值电压。BL1的上升受到BL2下降的影响,但由于逆耦合,BL1电平不会超过目标电平。反驱方案提高了BL建立和TPGM效率。通过将VTH分布的改进转化为程序时间的减少,可以减少大约10%的编程时间。

AUSP方案通过收紧单元的VTH分布来降低tPROG。编程脉冲之前有一个未选择字符串预充电(USP)周期来初始化所有通道。USP通过VDD对沟道预充电来防止程序脉冲中沟道升压不足,但会产生热载流子注入(HCI)扰动,如图28.2.2(a)所示。将低于VPASS (VLOW)的电压施加到所有WL,并关闭VTH高于VLOW的选定单元。源极选择线(SSL)侧沟道被预充到VDD,漏极选择线(DSL)侧沟道未被驱动。由于SSL端和DSL端通道之间的电压差,高电场会产生HCI扰动。在AUSP方案中,SSL端虚拟WL由VDWL控制,VDWL - VTH(DummyCell)应用于通道。由于较低的电场,HCI干扰减少。

图28.2.2(b)显示了与程序循环数成正比的增量通道初始化电压。通道初始化电压对应SSL侧沟道电压;较高的程序循环需要较高的通道初始化电压。通道初始化电压可以降低较低的程序循环,从而进一步减少HCI干扰。如图28.2.2(c)所示,编程后单元的VTH分布变宽,而AUSP编程后的VTH分布较常规USP窄。VTH分布的减少有助于减少约2%的tPROG。

PDS方案通过编写虚拟字符串的虚拟单元来减少tR和tPROG。DSL是按DSL切割来划分的,如图28.2.3(a)所示,它将每个DSL分开;同时,虚拟WL、主WL和SSL连接到3D-NAND单元阵列中的几个串。由DSL切割产生的虚拟串在WL上升/下降的情况下充当容性负载;因此,延迟了WL稳定时间。

图28.2.3(b)和28.2.3(c)给出了非编程虚拟字符串和编程虚拟字符串之间的不同通道条件。在一个未编程的虚拟串中,所有的单元都被打开,当VPASS应用于所有的WL时,通道电压通过源线电压(VSL)变为0V。非浮动通道作为容性负载,并影响WL建立时间。PDS方案将虚拟串SSL侧虚拟单元的VTH编程为高于VPASS,以关闭虚拟单元。当SSL端虚拟单元关闭,浮动通道不再作为容性负载,WL建立时间减少。

APR方案通过减少WL上升时间来降低tR。每个WL的电阻和电容特性不同,需要将不同的VPASS源连接到每个WL组,并由开关电路选择一个源。如图28.2.4(a)所示,在常规方案中,选择一个目标VPASS源并在VPASS上升时间应用于专用WL。如图28.2.4(b)所示,APR方案将VPASS上升时间分为A和B两部分,在A部分中,所有VPASS源都连接到所有WL,以减少WL上升时间。在B部分中,将一个目标VPASS源应用于专用WL,使其与传统的VPASS上升方案相同。APR方案降低了约2%的tR。

随着编程/擦除(P/E)周期的增加,错误位的数量也会增加;通过调整读取电压偏置可以减少错误比特数。改变读电平的读重试(RR)方案是克服这些情况的一种有效方法。然而,在常规RR中,只有当NAND设备中所有平面的读操作都完成时,才能改变读取电平。因此,读取性能取决于最后终止的平面。在这项工作中,使用PLRR方案来缓解NAND控制器的读性能下降。图28.2.5给出了一个PLRR序列示例:不管其他平面上发生了什么操作,读取电平都会发生变化。因此,可以立即发出后续的读命令,从而提高了读性能。此外,当平面的数量增加时,PLRR效应变得更大。

本文介绍了五种新技术,利用单元阵列架构下的外设电路实现高性能1Tb 3bit/cell 3D-NAND闪存。如图28.2.6所示的关键比较表报告了20Gb/mm2的比特密度,这是通过使用超过300个堆叠的WL来实现的,与之前的工作相比,它提高了程序吞吐量、tR和比特密度。所制造的TLC NAND芯片的模具显微照片如图28.2.7所示。

除了SK海力士以外,Intel也在ISSCC 2023上发布了一个与NAND Flash发展有关的论文,但该论文是从密度方面探索存储的升级。我们同样提供给大家参考。以下为文章译文:

1.67Tb、5b/Cell闪存采用192层浮栅3D-NAND技术具有23.3Gb/mm2比特密度

多代4b/cell (QLC)浮栅3D NAND技术的成功部署为QLC在整个行业的采用铺平了道路[1-4]。向5b/cell (PLC)的过渡将是加速比特密度(位密度)增长和将闪存扩展到更广泛市场的另一块垫脚石,在这些市场中,以合理的性能降低成本是最重要的要求。

在本文中,我们提出了第一个采用192层浮栅(FG)技术制造的PLC NAND芯片。芯片容量为1.67Tb,面积为73.3mm²,位密度为23.3Gb/mm²。该芯片还可以配置为1.33Tb QLC或1Tb 3b/cell (TLC),实现18.6Gb/mm²和14.0Gb/mm²的比特密度,比之前报道的最佳QLC[4]和TLC[5]比特密度提高24%和21%。图28.1.1显示了比特密度随层数的缩放趋势,表明与其他QLC实现相比,该方法具有更高的缩放效率。我们描述了实现可靠PLC运行的关键创新,以及支持系统级使用的功能,包括能够处理存在缺陷BLs的快速软位读取算法/快速读取校准算法、改善读取裕度的反向读取波形、SLC写通和程序挂起,以及一种与上述读操作兼容的恢复算法。

在有限的阈值电压窗口内,编程32个状态来编码每个单元5b的数据,这是一个重大的挑战。为了尽量减少来自相邻WLs的干扰,我们使用了两遍粗/精编程算法。与遭受氮化层中横向电荷扩散的电荷陷阱Flash技术相比,浮栅技术对电荷损耗的弹性是增加每个单元比特数的关键因素。然而,由于多晶硅沟道和接口中的陷阱,这两种技术都受到随机电报噪声(RTN)的影响,从而对状态可以放置的紧密程度施加了下限。

如图28.1.2所示,减小程序门阶长是以增加程序时间为代价来收紧TLC和QLC的阈值电压分布的有效方式;然而,与QLC通常使用的方法相比,它提供的好处越来越少。因此,为了可靠地读取数据,需要提高纠错码(ECC) 能力。与TLC相比,大多数QLC实现已经增加了ECC字节数。然而,为了避免面积损失,我们保持了ECC字节数不变,并使用快速软位读取(FSBR)算法增强了ECC校正能力。为了最大化2b中可以编码的信息(包括硬位数据共3b),我们实现了一个7选通读取算法,该算法将位从最强到最弱的置信度分为四个区间。

如图28.1.3所示,这是通过在不同的感应电流而不是不同的WL电压下感应电池来实现的,通过在放电后根据BL电流的比例调制施加到感应电容器背面的电压。该FSBR的平均读取时间(tR)为354μs,采用6-6-7-6-6格雷码将最大读取时间限制在386μs。

NAND-Flash存储器通常包括额外的冗余列,以修复有缺陷的BLs。在这项工作中,为了进一步减小芯片面积,我们将冗余列的数量减少了70%以上,并允许未修复的缺陷BLs出现在一小部分芯片中,只要未修复的BLs对原始比特误码率(RBER)的贡献显著小于错误修正能力。然而,未修复的缺陷BLs的存在会对软读操作的质量产生不利影响,因为这些位被感知为最强的0和1。为了避免这种情况,在读取算法中加入了特殊的开路/短路操作,以识别有缺陷的BLs,并将其置于最弱置信度区间,如图28.1.3所示。

随着阈值电压状态之间的紧密间隔,将读取电平放置在相邻状态之间的最佳位置是极其重要的。虽然在NAND制造过程中设置了最佳读取水平,但不能完全补偿NAND操作寿命期间和交叉温度(x-temp)条件下的裸片到裸片的变化。为了解决这个问题,我们实现了一个5选通快速读取校准算法,通过调制施加到传感电容器背面的电压,并计算在选通之间翻转的比特数。实验数据表明,该方案比之前提出的3选通算法精度更高。此外,与基于对属于不同状态的总位数的算法相比,本文算法不需要完全均匀的阈值电压分布,随着状态数的增加,阈值电压分布难以实现。图28.1.4显示了RBER分布;从而证明了所提出的算法即使在x-temp条件下也能使RBER远低于ECC校正能力的鲁棒性。

为了进一步提高读取裕度并降低RBER,采用了反向读取波形,如图28.1.5所示。传统上,采用反向读取的动机是通过避免通电压缓慢下降到最低读取电平来降低tR,这存在于正向读取波形中。然而,在这项工作中,主要的动机是提高较高读取级别的读取裕量,而对较低级别的影响可以忽略不计:如图28.1.5所示的实验数据。使用正向读取波形,具有较高阈值电压的单元在早期读取水平期间保持在耗尽状态,与它们被感知的反转状态相比,陷阱占用率显著不同。反向波形通过在相应的感测操作之前将这些单元维持在反转状态来提高读取裕度。

为了实现平衡的格雷码,在编程算法的第一次和第二次传递中都需要所有五页数据。虽然这是除[1]之外的大多数QLC实现的标准,但它要求在DRAM或类似介质中每个芯片存储几兆字节的数据。相反,我们在NAND芯片上使用1b/cell (SLC)缓存来存储两遍PLC编程算法所需的数据。为了保持SLC缓存的面积开销小于2%,我们将SLC的可靠性提高到了250k编程/擦除(P/E)周期,相当于目前PLC工作中1k的P/E周期能力。

暂停程序算法以服务读取请求的能力对于企业级混合工作负载极其重要。为了最小化静态页面缓冲区(SPB)区域,除了QLC程序操作所需的数据外,我们没有添加额外的数据锁存,并在程序算法期间将抑制信息编码为擦除数据(L0)。为了在编程暂停期间支持FSBR,每个BL至少需要3个数据锁存。

为了实现这一点,我们依赖于一个事实,即SLC缓存中有一个正在编程的数据副本可用。当接收到程序暂停命令时,die通过在数据锁存器之间执行逻辑与操作来构造抑制信息(INH),将INH保留在其中一个锁存器中,并释放其余的锁存器用于读取操作。为了恢复程序操作,首先从SLC缓存中读取用户数据,通过逻辑或操作与INH信息结合,然后恢复到相应的数据锁存器,如图28.1.6所示。

图28.1.7显示了制造好的NAND芯片的芯片照片,沿着本工作的关键指标。

报名提醒

2023 中国汽车半导体新生态论坛 (明天见)相关问答

E4421怎么输出方波?要输出方波,您需要使用计时器或示波器以及适当的硬件电路。以下是一种可能的方法:1.使用函数发生器或计时器来提供一个周期性的信号作为基准信号。调整基准信...

各位童鞋 急需帮忙!沭阳XRF分析仪推荐,XRF分析仪怎么选?[回答]一个高灵敏度和低噪声的接收机,并且使用了sourc-pull功能和二端口校准来消除失配和线损,测量结果理论上应该是最准确的,未来应该可以取代...我用的...