NAND Flash与NOR Flash究竟有何不同|半导体行业观察

来源:内容由 微信公众号 半导体行业观察 (ID:icbank) 翻译自「embedded」,作者 Avinash Aravindan,谢谢。

嵌入式系统设计人员在选择闪存时必须考虑许多因素:使用哪种类型的Flash架构,是选择串行接口还是并行接口,是否需要校验码(ECC)等。如果处理器或控制器仅支持一种类型的接口,则会限制选项,因此可以轻松选择内存。但是,情况往往并非如此。例如,一些FPGA支持串行NOR闪存、并行NOR闪存和NAND闪存来存储配置数据,同样,它们也可以用来存储用户数据,这使得选择正确的存储器件更加困难。本文将讨论闪存的不同方面,重点放在NOR闪存和NAND闪存的差异方面。

存储架构

闪存将信息存储在由浮栅晶体管制成的存储单元中。这些技术的名称解释了存储器单元的组织方式。在NOR闪存中,每个存储器单元的一端连接到源极线,另一端直接连接到类似于NOR门的位线。在NAND闪存中,几个存储器单元(通常是8个单元)串联连接,类似于NAND门(参见图1)。

NOR Flash(左)具有类似NOR门的架构。NAND Flash(右)类似于NAN

NOR Flash架构提供足够的地址线来映射整个存储器范围。这提供了随机访问和短读取时间的优势,这使其成为代码执行的理想选择。另一个优点是100%已知的零件寿命。缺点包括较大的单元尺寸导致每比特的较高成本和较慢的写入和擦除速度。

相比之下,与NOR闪存相比,NAND闪存具有更小的单元尺寸和更高的写入和擦除速度。缺点包括较慢的读取速度和I / O映射类型或间接接口,这更复杂并且不允许随机访问。值得注意的是,NAND Flash中的代码执行是通过将内容映射到RAM来实现的,这与直接从NOR Flash执行代码不同。另一个主要缺点是存在坏块。NAND闪存通常在部件的整个生命周期内出现额外的位故障时具有98%的良好位,因此,器件内需要ECC功能。

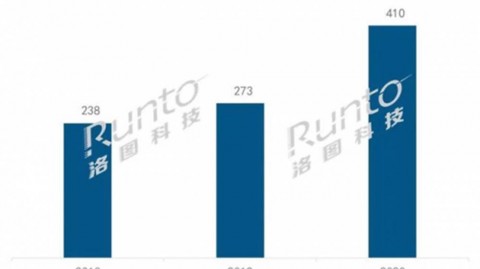

存储容量

与NOR闪存相比,NAND闪存的密度要高得多,主要是因为其每比特成本较低。NAND闪存通常具有1Gb至16Gb的容量。NOR闪存的密度范围从64Mb到2Gb。由于NAND Flash具有更高的密度,因此主要用于数据存储应用。

擦除/读写

在NOR和NAND闪存中,存储器被组织成擦除块。该架构有助于在保持性能的同时保持较低的成本,例如,较小的块尺寸可以实现更快的擦除周期。然而,较小块的缺点是芯片面积和存储器成本增加。由于每比特成本较低,与NOR闪存相比,NAND闪存可以更经济高效地支持更小的擦除块。目前,NAND闪存的典型块大小为8KB至32KB,NOR Flash为64KB至256KB。

NAND闪存中的擦除操作非常简单,而在NOR闪存中,每个字节在擦除之前都需要写入“0”。这使得NOR闪存的擦除操作比NAND闪存慢得多。例如,NAND闪存S34ML04G2需要3.5ms才能擦除128KB块,而NOR闪存S70GL02GT则需要约520ms来擦除类似的128KB扇区。这相差近150倍。

如前所述,NOR闪存具有足够的地址和数据线来映射整个存储区域,类似于SRAM的工作方式。例如,具有16位数据总线的2Gbit(256MB)NOR闪存将具有27条地址线,可以对任何存储器位置进行随机读取访问。在NAND闪存中,使用多路复用地址和数据总线访问存储器。典型的NAND闪存使用8位或16位多路复用地址/数据总线以及其他信号,如芯片使能,写使能,读使能,地址锁存使能,命令锁存使能和就绪/忙碌。NAND Flash需要提供命令(读,写或擦除),然后是地址和数据。这些额外的操作使NAND闪存的随机读取速度慢得多。例如,NAND闪存S34ML04G2需要30μS,而NOR闪存S70GL02GT需要120nS。因此,NOR比NAND快250倍。

为了克服或减少较慢读取速度的限制,通常以NAND闪存中的页方式读取数据,每个页是擦除块的较小子部分。仅在每个读取周期开始时使用地址和命令周期顺序读取一页的内容。NAND闪存的顺序访问持续时间通常低于NOR闪存设备中的随机访问持续时间。利用NOR Flash的随机访问架构,需要在每个读取周期切换地址线,从而累积随机访问以进行顺序读取。随着要读取的数据块的大小增加,NOR闪存中的累积延迟变得大于NAND闪存。因此,NAND Flash顺序读取可以更快。但是,由于NAND Flash的初始读取访问持续时间要长得多,两者的性能差异只有在传输大数据块时才是明显的,通常大小要超过1 KB。

在两种Flash技术中,只有在块为空时才能将数据写入块。NOR Flash的慢速擦除操作使写操作更慢。在NAND Flash中,类似于读取,数据通常以页形式编写或编程(通常为2KB)。例如,单独使用NAND闪存S34ML04G2 写入页面需要300μS。

为了加快写入操作,现代NOR Flashes还采用类似于页面写入的缓冲区编程。例如,前文所述的NOR闪存S70GL02GT,支持缓冲器编程,这使其能够实现与单词相似写入超时多字节编程。例如,512字节数据的缓冲区编程可以实现1.14MBps的吞吐量。

能耗

NOR闪存在初始上电期间通常需要比NAND闪存更多的电流。但是,NOR Flash的待机电流远低于NAND Flash。两个闪存的瞬时有功功率相当。因此,有效功率由存储器活动的持续时间决定。NOR Flash在随机读取方面具有优势,而NAND Flash在擦除,写入和顺序读取操作中消耗的功率相对较低。

可靠性

保存数据的可靠性是任何存储设备的重要性能指标。闪存会遭遇称为位翻转的现象,其中一些位可以被反转。这种现象在NAND闪存中比在NOR闪存中更常见。出于产量考虑,NAND闪存随附着散布的坏块,随着擦除和编程周期在NAND闪存的整个生命周期中持续,更多的存储器单元变坏。因此,坏块处理是NAND闪存的强制性功能。另一方面,NOR闪存带有零坏块,在存储器的使用寿命期间具有非常低的坏块累积。因此,当涉及存储数据的可靠性时,NOR Flash具有优于NAND Flash的优势。

可靠性的另一个方面是数据保留,这方面,NOR Flash再次占据优势,例如,NOR Flash闪存S70GL02GT提供20年的数据保留,最高可达1K编程/擦除周期,NAND闪存S34ML04G2提供10年的典型数据保留。

编程和擦除周期的数量曾是一个需要考虑的重要特性。这是因为与NOR闪存相比,NAND闪存用于提供10倍更好的编程和擦除周期。随着技术进步,这已不再适用,因为这两种存储器在这方面的性能已经很接近。例如,S70GL02GT NOR和S34ML04G2 NAND都支持100,000个编程 - 擦除周期。但是,由于NAND闪存中使用的块尺寸较小,因此每次操作都会擦除较小的区域。与NOR Flash相比,其整体寿命更长。

表1提供了本文中讨论的主要内容摘要。

NOR闪存和NAND闪存的主要特性与一般和具体比较数据的比较。

通常,NOR闪存是需要较低容量、快速随机读取访问和更高数据可靠性的应用的理想选择,例如代码执行所需。NAND闪存则非常适用于需要更高内存容量和更快写入和擦除操作的数据存储等应用。

TMS320C6678 DSP + Xilinx Kintex-7 FPGA核心板硬件参数资源说明分享

硬件资源

SOM-TL6678F核心板板载DSP、FPGA、CPLD、ROM、RAM、晶振、电源、LED等硬件资源,并通过工业级高速B2B连接器引出IO。

图 1 核心板硬件框图

图 2

图 3

DSP

核心板DSP型号兼容TMS320C6678ACYPA25(1.25GHz)、TMS320C6678ACYPA(1GHz),FCBGA(841)封装,工作温度为-40°C~100°C,引脚数量为841个,尺寸为24mm*24mm。

TI TMS320C6678处理器架构如下:

图 4 TMS320C6678处理器功能框图

FPGA

核心板FPGA型号为XC7K325T-2FFG676I,FFG676封装,工作温度范围为-40°C~100°C,引脚数量为676个,尺寸为27mm*27mm。

Kintex-7系列FPGA特性如下所示:

图 5 Kintex-7系列FPGA特性

ROM

NAND FLASH

核心板DSP通过EMIF16总线连接工业级NAND FLASH,采用8bit数据线,型号为S34MS01G2,容量为128MByte。

SPI NOR FLASH

核心板DSP通过SPI总线连接工业级SPI NOR FLASH,型号兼容GigaDevice公司的GD25WQ128E和Micron公司的MT25QU128ABA,容量为128Mbit。

核心板FPGA通过SPI总线连接工业级SPI NOR FLASH,型号为MT25QU256ABA,容量为256Mbit。

EEPROM

核心板DSP通过I2C总线连接工业级EEPROM,型号为AT24CM01,容量为1Mbit,I2C地址为0x50。

备注:DSP I2C总线在核心板内部已连接EEPROM,用于存储IBL引导程序。从系统稳定性角度考虑,建议进行底板设计时尽量选用其他通信总线完成功能设计。

RAM

核心板DSP通过专用DDR EMIF Data Bus总线连接4片工业级DDR3,每片采用16bit数据线,共64bit。DDR3型号兼容MT41K128M16(256MByte)和MT41K256M16(512MByte),支持DDR3-1333工作模式(667MHz)。

核心板DSP通过专用DDR3_EMIF Check Bit总线连接1片工业级DDR3(作为ECC内存),采用8bit数据线,DDR3型号兼容MT41K128M16(256MByte)和MT41K256M16(512MByte)。

核心板FPGA通过BANK 33、BANK 34连接2片工业级DDR3,每片采用16bit数据线,共32bit。DDR3型号兼容MT41K128M16(256MByte)、MT41K256M16(512MByte),支持DDR3-1066工作模式(533MHz)。

晶振

核心板采用3个工业级晶振U15、U17和U18,为板载DSP提供系统时钟源。其中U15晶振和U17晶振时钟频率均为25MHz,精度为±25ppm,用作板载CDCM61002时钟芯片的时钟源。U18晶振时钟频率为50MHz,精度为±25ppm,经转换为差分时钟后为DSP的DDR控制器提供时钟源。

核心板采用3个工业级晶振U30、U31和U34,为板载FPGA提供系统时钟源。其中U30晶振为SCJO05-250001820B30Q,时钟频率为25MHz,精度为±50ppm,通过IO_L13P_T2_MRCC_14引脚为FPGA提供系统时钟源。U31、U34晶振为7X25000010,时钟频率为25MHz,精度为±25ppm,用作板载CDCM61002时钟芯片的时钟源。

核心板采用工业级晶振U45为板载CPLD提供系统时钟源。U45晶振时钟频率为25MHz,精度为±50ppm。

时钟芯片

DSP时钟系统

核心板DSP端时钟系统采用2个工业级CDCM61002时钟芯片。一个由U15晶振输入25MHz时钟源,倍频后产生两路100MHz差分时钟,分别向DSP的CORECLK、PASSCLK和PCIECLK提供时钟输入。另一个由U17晶振输入25MHz时钟源,倍频后产生两路250MHz差分时钟,分别向DSP的SRIOSGMII和HyperLink提供时钟输入。

核心板DSP PCIe接口支持同源时钟模式和非同源时钟模式。其中非同源时钟模式采用板载CDCM610002时钟芯片输出的100MHz时钟源,同源时钟模式采用评估底板PCIe接口输入的时钟源。

FPGA时钟系统

核心板FPGA端时钟系统采用2个工业级CDCM61002时钟芯片,时钟系统框图如下所示。

图 6

一个CDCM61002时钟芯片由U31晶振输入25MHz时钟源,默认通过下图硬件配置电路,倍频后产生两路100MHz差分时钟,分别向FPGA的BANK 115 GTX0输入和BANK 116 GTX1输入提供时钟源。

同时可通过FPGA IO对该时钟芯片进行配置,修改输出的时钟频率。

图 7

图 8

另一个由U34晶振输入25MHz时钟源,通过下图硬件配置电路,倍频产生两路200MHz差分时钟,向FPGA的IO_L13P_T2_MRCC_34/IO_L13N_T2_MRCC_34提供DDR时钟源,向FPGA的IO_L12P_T1_MRCC_34/IO_L12N_T1_MRCC_34提供用户时钟源。

图 9

图 10

电源

核心板采用分立电源供电设计,所选电源方案均满足工业级环境使用要求。电源系统设计满足板载DSP、FPGA的供电要求,通过核心板板载CPLD程序控制电源使能,满足上电时序要求。核心板采用9V直流电源供电。

CPLD

核心板板载CPLD,出厂时已经固化用于控制核心板DSP、FPGA上电时序的程序,用户可无需进行CPLD程序开发。

LED

核心板板载7个LED。其中LED0为电源指示灯,在核心板供电后默认点亮。LED8为CPLD状态指示灯,在核心板DSP上电复位完成后点亮。LED1和LED2为DSP端用户可编程指示灯,分别对应GPIO14和GPIO15两个引脚,高电平点亮。LED3和LED4为FPGA端用户可编程指示灯。LED5为FPGA DONE指示灯,当FPGA初始化完成后会点亮。

图 11

图 12

图 13

图 14

温度传感器

核心板DSP通过I2C总线连接一个温度传感器,型号为TMP102AIDRLT,I2C地址为0x49。

图 15

核心板FPGA端通过I2C总线连接一个温度传感器,型号为TMP102AIDRLT,I2C地址为0x48。

图 16

B2B连接器

核心板采用4个申泰(Samtec)公司的工业级高速B2B连接器,共720pin,间距0.5mm,合高5.0mm。包含2个180pin公座B2B连接器,型号BTH-090-01-L-D-A-K-TR,高度4.27mm。2个180pin母座B2B连接器,型号BSH-090-01-L-D-A-TR,高度3.25mm。B2B连接器单端最高通信速率为18Gbps,差分最高通信速率为19Gbps。

图 17

外设资源

核心板DSP端B2B连接器引出的主要外设资源及性能参数如下表所示。

引脚说明

引脚排列

核心板B2B连接器分别为CON0A(对应评估底板CON0A)、CON0B(对应评估底板CON0B)、CON0C(对应评估底板CON0C)、CON0D(对应评估底板CON0D),引脚排列如下图所示。

图 18 核心板引脚排列示意图

引脚定义

核心板B2B连接器引脚定义如下表。

其中“B2B引脚号”为核心板B2B连接器引脚序列号,“芯片引脚号”为DSP/FPGA引脚序列号,“引脚信号名称”为DSP/FPGA引脚信号名称,NC表示该引脚信号未连接到DSP/FPGA引脚,“引脚功能”为核心板引脚推荐功能描述。

内部引脚说明

“B2B引脚号”NC表示核心板该内部引脚未引出到B2B连接器,其他代表内部已使用且同时引出到核心板B2B连接器。

DSP处理器在核心板内部通过SRIO、EMIF16、I2C、GPIO与FPGA相连,具体引脚连接关系如下表所示。

表格“连接方向”列中"->"指信号流向从DSP至FPGA,"<-"指信号流向从FPGA至DSP,"<->"指信号可在DSP及FPGA双向流通。

引脚上下拉说明

下表为核心板内部已作上下拉配置引脚的说明。表中未说明的引脚,核心板内部默认未作上下拉配置,直接引出到B2B连接器。

电气特性

工作环境

表 7

环境参数

最小值

典型值

最大值

工作温度

-40°C

/

85°C

存储温度

-50°C

/

90°C

工作湿度

35%(无凝露)

/

75%(无凝露)

存储湿度

35%(无凝露)

/

75%(无凝露)

工作电压

/

9.0V

/

功耗测试

表 8

工作状态

电压典型值

电流典型值

功耗典型值

状态1

9.0V

0.86A

7.74W

状态2

9.0V

2.14A

19.26W

备注:功耗基于TL6678F-EasyEVM评估板(核心板型号:SOM-TL6678F-1000/325T-8/4GD-I-A2)测得。功耗测试数据与具体应用场景有关,仅供参考。

状态1 :评估板不接入外接模块,DSP运行LED测试例程,FPGA运行资源利用率较低的LED测试例程。

状态2: 评估板不接入外接模块,DSP运行FFT测试程序,8个C66x核心的资源使用率约为100%;FPGA运行资源利用率较高的IFD综合功能测试程序,电源功率约为6.946W,资源利用率如下图所示。

图 19

热成像图

核心板在常温环境、“状态2”的条件下稳定工作10min后,分别在增加散热器(不开启风扇)、增加散热器(开启风扇)的情况下,测得核心板热成像图如下所示。H为最高温度,S为平均温度。

备注:不同测试条件下结果会有所差异,数据仅供参考。

图 20 安装散热器(不开启风扇)

图 21 安装散热器(开启风扇)

请参考以上测试结果,并根据实际情况合理选择散热方式。

机械尺寸

表 9

PCB尺寸

75mm*112mm

PCB层数

14层

安装孔

4个

元器件最高高度

3.0mm

PCB板厚

2.0mm

B2B连接器合高

5.0mm

图 22

图 23

元器件最高高度:指核心板最高元器件水平面与PCB正面水平面的高度差。核心板最高元器件为DSP(U1)。

底板设计注意事项

最小系统设计

基于SOM-TL6678F核心板设计底板时,请务必满足最小系统设计要求,具体如下。

电源设计说明

VDD_9V_SOMVDD_9V_SOM(VDD_9V_BRD)为核心板的主供电输入。如产品一般在室温环境下使用,核心板电源功率建议参考评估板按最大27W进行设计;如产品一般在高温环境下使用,核心板电源功率建议按最大40W进行设计。

图 24

VDD_9V_SOM在核心板内部未预留总电源输入的储能大电容,底板设计时请参照评估板原理图,在靠近B2B连接器位置放置储能大电容。

图 25

VDD_1V8_BRD

VDD_1V8_BRD为底板提供的外设电源。由于核心板采用官方推荐的"IO Before Core Power Sequencing"上电时序,所以VDD_1V8_BRD与VDD_9V_SOM同时上电。

图 26

图 27

FPGA端BANK电源设计

核心板内部已将BANK 0、BANK 14、BANK 16电平配置为1.8V,同时将BANK 33、BANK 34电平配置为1.5V。

BANK 12、BANK 13、BANK 15供电可在底板灵活配置,可根据实际需要选择1.5V、1.8V、2.5V或3.3V供电,最高不得超过3.45V。BANK 32为HP BANK,根据实际需要选择1.5V、1.8V供电。

XADC电源

XADC电源引脚VCCADC_0在核心板内部已连接到1.8V,XADC参考电压输入引脚XADC_VREF_0在核心板内部已经接GNDADC_0,此时将默认使用FPGA内部参考电压,同时该引脚通过0R电阻(默认空贴)引出到B2B。

VCCBATT电源

核心板设计默认不使用VCCBATT电源,该引脚已在核心板内部设计1K下拉电阻到GND。

系统启动配置

核心板由板载CPLD引出SYS_BOOTSET[1:5]共5位BOOTSET引脚,通过CPLD控制DSP端及FPGA端系统启动配置。

用户可参考评估底板SYS_BOOTSET部分电路(如下图),以及相关配置说明进行电路设计即可。

图 28

SYS_BOOTSET[1:3]为DSP端启动配置设置位。

由于DSP端BOOTSET引脚与GPIO信号存在复用关系,如使用GPIO外接设备,请保证DSP在上电初始化过程中BOOTSET引脚电平不受外接设备的影响,否则将会导致DSP无法正常启动。

SYS_BOOTSET[4]为DSP PCIe接口同源时钟及非同源时钟选择设置位。

板载DSP PCIe接口支持非同源时钟模式和同源时钟模式,核心板引出SYS_BOOTSET[4]引脚进行选择配置,0为非同源模式,1为同源模式。其中非同源时钟模式采用板载CDCM610002时钟芯片输出的100MHz时钟源,同源时钟模式采用评估底板PCIe接口输入的时钟源。

SYS_BOOTSET[5]为FPGA端启动配置设置位。

0为Master SPI模式,此时FPGA可进行程序在线加载、固化并离线启动。1为Slave Serial模式,此时DSP可通过SPI总线在线加载FPGA程序。

系统复位信号

RESETFULLZ

RESETFULLZ(DSP_RSTFULL)为DSP的复位输入引脚,该复位信号不但复位所有寄存器,还将复位所有调试环境。底板设计时应增加10K上拉电阻。

RESETZ

RESETZ为DSP的WARM RESET复位输入引脚,该复位信号会复位除调试环境以外的所有功能逻辑。底板设计时应增加10K上拉电阻。

nNMI

nNMI(DSP_NMIZ)为DSP不可屏蔽中断引脚,底板设计时应增加10K上拉电阻。

PROGRAM

PROGRAM_B(FPGA_PROG)信号用于复位FPGA逻辑。核心板未经过处理直接引出到B2B,不使用时注意使用上拉将其电平固定。

SYS_nRESET

SYS_nRESET信号连接核心板内部CPLD,当该信号被拉低时,CPLD将控制DSP、FPGA重新上电,不使用时注意使用上拉将其电平固定。

设计注意事项:

DSP的RESETFULLZ、RESETZ、PORZ引脚在核心板内部已连接到CPLD。当DSP完成上电后,CPLD将与DSP的RESETFULLZ、RESETZ、PORZ引脚相连的IO配置为高阻态,并且使能CPLD相连引脚的内部上拉电阻,将RESETFULLZ、RESETZ、PORZ引脚固定为高电平。

其他配置信号

PUDC_B

BANK 14中的PUDC_B引脚为FPGA IO启动上拉使能配置引脚,在核心板内部已设计1K下拉电阻到GND,并通过核心板B2B连接器引出。

图 29

CFGBVS配置说明

FPGA的CFGBVS引脚在核心板中已直连1.8V电源,下图为CFGBVS的配置说明。

图 30

图 31

其他设计注意事项

保留风扇控制电路

由于核心板功耗较高,请使用风扇方式进行散热,底板设计时建议保留风扇控制电路。

保留UART接口

评估底板将核心板DSP的UART_RXD和UART_TXD引脚通过CP2105芯片引到Micro USB接口,作为DSP端系统调试串口使用。底板设计时,建议保留UART作为系统调试串口。

评估底板将核心板FPGA的引脚通过CP2105芯片引到Micro USB接口上,作为FPGA端系统调试串口使用。底板设计时,建议保留F/H9/UART1_RXD_16/1V8(IO_L1P_T0_16)、F/H8/UART1_TXD_16/1V8(IO_L1N_T0_16)分别作为系统调试串口的RX与TX。

保留JTAG接口

评估底板引出14pin 2.54mm间距DSP端JTAG接口,引出14pin 2.0mm间距FPGA端JTAG接口。为便于系统的调试,底板设计时建议保留DSP与FPGA端的JTAG调试接口。

FMC接口LA信号不等长问题

存在问题:由核心板引出的FMC1、FMC2接口的LA信号未严格按照等长设计,在进行高速信号通信时可能会造成通信时序不对齐,从而影响通信质量。

使用说明:底板设计时,FMC接口信号等长设计请勿超过+/-100mil。如产品已成型,且LA信号未严格按照等长设计,可考虑通过软件进行时序优化。

相关问答

用 FPGA 怎样实现将模拟量转换成数字量? - 勿失勿忘_cn 的回答...fpga不能直接实现模拟量转换成数字量,这一功能要由AD转换芯片完成,FPGA可以将AD芯片转换的结果读出来,即是模拟量转换成的数字量的值。FPGA是一中数...

盆友们,谁了解!!徐州非家政的衣橱整理师授课,衣橱整理师...[回答](1)整理;整治整法度。(整顿法令制度。)——《后汉书·张衡传》整羁鞘。——《资治通鉴·唐纪》(2)又如:整旅(整顿军队);整比(整理排比);整弁(整冠);...