总线基本概念、设计要素 、设计要素、标准与互连结构

总线在各层次上提供部件之间的连接和交换信息通路 分为以下几类:

• 芯片内总线:在芯片内部各元件之间提供连接 在芯片内部各元件之间提供连接 - 例如,CPU芯片内部,各寄存器、ALU、指令部件等之间有总线相连 、指令部件等之间有总线相连 • 系统总线:在系统主要功能部件 在系统主要功能部件 在系统主要功能部件(CPU 、MM和各种I/O控制器)间提供连接 -

单总线结构 – 将CPU、MM和各种I/O适配卡通过底板总线(Backplane Bus)互连,底板总 线为标准总线(Industry standard) -

多总线结构 – 将CPU、Cache、MM和各种I/O适配卡用局部总线、 适配卡用局部总线、处理器-主存总线、高 速I/O总线、扩充I/O总线等互连。主要有两大类: Processor- Memory Bus (Design specific or proprietary) » 短而快,仅需与内存匹配 仅需与内存匹配 仅需与内存匹配,使CPU-MM之间达最大带宽 I/O Bus (Industry standard) » 长而慢,需适应多种设备 需适应多种设备 需适应多种设备,一侧连接到Processor- Memory Bus 或 Backplane Bus,另一侧连到I/O控制器 (注:Intel公司在推出845、850等芯片组时,对“System Bus”有专门的定义, 有专门的定义,将 处理器总线称为前端总线(Front Bus)或系统总线)

• 通信总线:在主机和I/O设备之间或计算机系统之间提供连接 - 通常是电缆式总线, 通常是电缆式总线,如SCSI、RS-232、USB等

系统总线的组成

系统总线通常由一组 系统总线通常由一组控制线、一组数据线和一组地址线构成。也有些总线没有单独的地址 也有些总线没有单独的地址 线,地址信息通过数据线来传送 地址信息通过数据线来传送 地址信息通过数据线来传送,这种情况称为数据/地址复用。

• 数据线(Data Bus):承载在源和目部件之间传输的信息。 承载在源和目部件之间传输的信息。数据线的宽度反映一次能 数据线的宽度反映一次能 传送的数据的位数。 传送的数据的位数。

• 地址线(Address Bus) :给出源数据或目的数据所在的主存单元或I/O端口的地址。 地址线的宽度反映最大的寻址空间。 地址线的宽度反映最大的寻址空间。

• 控制线(Control Bus) :控制对数据线和地址线的访问和使用。 控制对数据线和地址线的访问和使用。用来传输定时信号 用来传输定时信号 和命令信息。典型的控制信号包括 典型的控制信号包括 典型的控制信号包括:

- 时钟(Clock):用于总线同步。 用于总线同步。

- 复位(Reset):初始化所有设备。 初始化所有设备。 - 总线请求(Bus Request):表明发出该请求信号的设备要使用总线。 表明发出该请求信号的设备要使用总线。

- 总线允许(Bus Grant):表明接收到该允许信号的设备可以使用总线。 表明接收到该允许信号的设备可以使用总线。

- 中断请求(Interrupt Request):表明某个中断正在请求。 表明某个中断正在请求。

- 中断回答(Interrupt Acknowledge) :表明某个中断请求已被接受。 表明某个中断请求已被接受。

- 存储器读(memory read):从指定的主存单元中读数据到数据总线上。 从指定的主存单元中读数据到数据总线上。

- 存储器写(memory write):将数据总线上的数据写到指定的主存单元中。 将数据总线上的数据写到指定的主存单元中。

- I/O读(I/O read):从指定的I/O端口中读数据到数据总线上。 端口中读数据到数据总线上。

- I/O写(I/O Write) :将数据总线上的数据写到指定的I/O端口中。

- 传输确认(transmission Acknowledge) :表示数据已被接收或已被送到总线

总线设计要素

总线设计要考虑的基本要素 总线设计要考虑的基本要素 尽管有许多不同的总线实现方式, 尽管有许多不同的总线实现方式,但总线设计的基本要素和考察的性能指标一样 但总线设计的基本要素和考察的性能指标一样

①信号线类型(Signal line type): 专用(Separate) / 复用(Multiplexed) ②仲裁方法(Arbitrating): 集中式(Center) / 分布式(distributed)

③定时方式(Timing): 同步通信 (Synchronous) / 异步通信 (Asynchronous)

④事务类型(Bus Transaction): 总线所支持的各种数据传输类型和其他总线操作类型, 总线所支持的各种数据传输类型和其他总线操作类型,如: 存储器读、存储器写、I/O读、I/O写、读指令、中断响应等

⑤总线带宽(Bus Bandwidth): 单位时间内在总线上传输的最大数据量( 单位时间内在总线上传输的最大数据量(是一种传输能力 是一种传输能力 是一种传输能力) 相当于公路的最大载客量。 相当于公路的最大载客量。例如,沪宁高速每车道最多每 沪宁高速每车道最多每5分钟发一辆车, 分钟发一辆车,每辆车 最多50人,共有6个车道,则最大流量为多少 则最大流量为多少 则最大流量为多少(?人/小时)? 最大载客量:6道x12车/小时x50人/车= 3600人/小时

信号线类型

总线的信号线类型有:

专用、复用 • 专用信号线: - 信号线专用来传送某一种信息。 例如,使用分立的数据线和地址线 ,使用分立的数据线和地址线,使得数据信息专门由数据线传 ,使得数据信息专门由数据线传 输,地址信息专门由地址线传输 地址信息专门由地址线传输。

• 复用信号线: - 信号线在不同的时间传输不同的信息。 例如,许多总线采用数据 ,许多总线采用数据/地址线分时复用方式,用一组数据线在总 ,用一组数据线在总 线事务的地址阶段传送地址信息,在数据阶段传送数据信息 ,在数据阶段传送数据信息。这样 就使得地址和数据通过同一组数据线进行传输。

• 信号分时复用的优缺点: - 优:减少总线条数,缩小体积、降低成本。 - 缺:总线模块的电路变复杂 总线模块的电路变复杂,且不能并行。

总线裁决(总线控制/使用/访问权的获得 /访问权的获得)

总线被多个设备共享,但每一时刻只能有一对设备使用总线传输信息 ,但每一时刻只能有一对设备使用总线传输信息。

什么是总线裁决 什么是总线裁决? 当多个设备需要使用总线进行通信时,采用某种策略选择一个设备使用总线 ,采用某种策略选择一个设备使用总线 °

为什么要进行总线裁决 为什么要进行总线裁决 ? 总线被连接在其上的所有设备共享,如果没有任何控制 ,如果没有任何控制,那么当多个设备需 ,那么当多个设备需 要进行通信时,每个设备都试图为各自的传输将信号送到总线上 ,每个设备都试图为各自的传输将信号送到总线上,这样就会 产生混乱。所以必须进行总线裁决 。所以必须进行总线裁决

如何避免上述混乱 如何避免上述混乱?

• 在总线中引入一个或多个总线主控设备,只能主控设备控制总线 ,只能主控设备控制总线 - 主控设备:能发起总线请求并控制总线 :能发起总线请求并控制总线。(如:处理器)

- 从设备:只能响应从主控设备发来的总线命令 :只能响应从主控设备发来的总线命令。(如:主存)

• 利用总线裁决决定哪个总线主控设备将在下次得到总线使用权

①总线裁决信号

①总线裁决信号: 总线请求线和总线许可线 : 总线请求线和总线许可线 总线请求线可以和数据线复用,但这样会影响带宽 ,但这样会影响带宽 如:数据线和总线请求线复用时 数据线和总线请求线复用时,总线裁决和数据传输不能同时进行 ,总线裁决和数据传输不能同时进行

②总线裁决有两种方式:集中式和分布式 :集中式和分布式 集中式:将控制逻辑做在一个专门的总线控制器或总线裁决器中,通过将所有 的总线请求集中起来利用一个特定的裁决算法进行裁决 菊花链(Daisy chain) 计数器定时查询(Query by a counter) 集中并行(Centralized, Parallel) 分布式:没有专门的总线控制器,其控制逻辑分散在各个部件或设备中 ,其控制逻辑分散在各个部件或设备中 自举式(Self-selection) 冲突检测 (Collision detection)

③裁决方案应在以下两个因素间进行平衡 等级性(Priority)—具有高优先级的设备应该先被服务 公平性(Fairness)—即使具有最低优先权的设备也不能永远得不到总线使用权

计数器定时查询裁决

°基本思想:比菊花链查询多一组设备线( 比菊花链查询多一组设备线(DevID),少一根总线允许线 ),少一根总线允许线BG。总线控制器接收 。总线控制器接收 到BR送来的总线请求信号后, 送来的总线请求信号后,在总线未被使用 在总线未被使用 在总线未被使用(Busy=0)的情况下,由计数器开始计数 由计数器开始计数 由计数器开始计数, 并将计数值通过设备线向各设备发出。 并将计数值通过设备线向各设备发出。当某个有总线请求的设备号与计数值一致时 当某个有总线请求的设备号与计数值一致时 当某个有总线请求的设备号与计数值一致时,该设备 便获得总线使用权, 便获得总线使用权,此时终止计数查询 此时终止计数查询 此时终止计数查询,同时该设备建立总线忙 同时该设备建立总线忙Busy信号。

优点: ① 灵活,设备的优先级可通过设置不同的计数初始值来改变 设备的优先级可通过设置不同的计数初始值来改变 设备的优先级可通过设置不同的计数初始值来改变。 若每次初值皆为0,则固定; 若每次初值总是刚获得总线使用权的设备, 若每次初值总是刚获得总线使用权的设备,则是平等的循环优先级方式 则是平等的循环优先级方式 则是平等的循环优先级方式。② 对电路故障不如菊花链查询那样敏感 对电路故障不如菊花链查询那样敏感。

缺点:① 需要增加一组设备线 ② 总线设备的控制逻辑变复杂(需对设备号进行译码比较等)

自举分布式裁决

• 优先级固定,各设备独立决定自己是否是最高优先级请求者 各设备独立决定自己是否是最高优先级请求者 • 需请求总线的设备在各自对应的总线请求线上送出请求信号 • 在总线裁决期间每个设备将比自己优先级高的请求线上的信号取回分析: 在总线裁决期间每个设备将比自己优先级高的请求线上的信号取回分析:

- 若有总线请求信号, 若有总线请求信号,则本设备不能立即使用总线 则本设备不能立即使用总线

- 若没有,则可以立即使用总线 则可以立即使用总线 则可以立即使用总线,并通过总线忙信号阻止其他设备使用总线 并通过总线忙信号阻止其他设备使用总线

- 最低优先级设备可以不需要总线请求线, 最低优先级设备可以不需要总线请求线,为什么?

- 需要较多连线用于请求信号, 需要较多连线用于请求信号,所以,许多总线用数据线 许多总线用数据线DB作为总线请求线 N个设备要多少请求信号? 个设备要多少请求信号? - NuBus(MacintoshII 中的底板式总线)、 中的底板式总线)、SCSI总线等采用该方案 上图中的优先级 (优先级)是什么?

冲突检测方式裁决

基本思想: 当某个设备要使用总线时,它首先检查一下是否有其他设备正在使用总线 ,它首先检查一下是否有其他设备正在使用总线 如果没有,那它就置总线忙 ,那它就置总线忙,然后使用总线 ,然后使用总线; 若两个设备同时检测到总线空闲,则可能会同时使用总线 ,则可能会同时使用总线,此时发生冲突 ,此时发生冲突; 一个设备在传输过程中,它会帧听总线以检测是否发生了冲突 ,它会帧听总线以检测是否发生了冲突; 当冲突发生时,两个设备都会停止传输 ,两个设备都会停止传输,延迟一个随机时间后再重新使用总线 ,延迟一个随机时间后再重新使用总线 - 该方案一般用在网络通信总线上,如:Ethernet总线等。

总线定时方式

什么是总线的定时 什么是总线的定时 通过总线裁决确定了哪个设备可以使用总线,那么一个取得了总线控制 ,那么一个取得了总线控制 权的设备如何控制总线进行总线操作呢?也即如何来定义总线事务中的 ?也即如何来定义总线事务中的 每一步何时开始、何时结束呢?这就是总线通信的定时问题 ?这就是总线通信的定时问题。 ° 总线通信的定时方式 总线通信的定时方式

• Synchronous (同步):用时钟来同步定时 :用时钟来同步定时

• Asynchronous(异步):用握手信号定时 用握手信号定时

• Semi-Synchronous (半同步):同步(时钟)和异步(握手信号)结合

• Split transaction(拆分事务):在从设备准备数据时,释放总线 处理器-存储器总线都采用同步方式 异步方式只有通信总线或I/O才会使用 I/O总线大多采用半同步方式 拆分事务方式可以提高总线的有效带宽

同步总线 (Synchronous Bus)

异步总线 (Asynchronous Bus)

非时钟定时,没有一个公共的时钟标准 ,没有一个公共的时钟标准。因此,能够连接带宽范围很大的各种 ,能够连接带宽范围很大的各种 设备。总线能够加长而不用担心时钟偏移 。总线能够加长而不用担心时钟偏移(clock skew)问题 ° 采用握手协议(handshaking protocol)即:应答方式。

• 只有当双方都同意时,发送者或接收者才会进入到下一步 ,发送者或接收者才会进入到下一步,协议通过一对 ,协议通过一对 附加的“握手”信号线(Ready、Ack)来实现 ° 异步通信有非互锁 异步通信有非互锁、半互锁和全互锁三种方式

• 优点:灵活,可挂接各种具有不同工作速度的设备 ,可挂接各种具有不同工作速度的设备 • 缺点: ① 对噪声较敏感 ① 对噪声较敏感(任何时候都可能接收到对方的应答信号 (任何时候都可能接收到对方的应答信号) ② 接口逻辑较复杂

Handshaking Protocol(握手协议 )

半同步总线

为解决异步方式对噪声敏感的问题, 为解决异步方式对噪声敏感的问题,在异步总线中引入时钟信号 在异步总线中引入时钟信号 就绪和应答等握手信号 (如:Wait信号、TRDY和IRDY信号等) 都在时钟的上升沿有效 信号的有效时间限制在时钟到达的时刻, 信号的有效时间限制在时钟到达的时刻,而不受其他时间的信号干扰 而不受其他时间的信号干扰

° 通过“Wait”信号从设备告知主设备何时数据有效 ° 结合了同步和异步的优点 结合了同步和异步的优点 结合了同步和异步的优点。既保持了“所有信号都由时钟定时”的特点, 又允许“不同速度设备共存于总线”

Split Bus Transaction(拆分总线事务 )

将一个事务分成两个子过程: 将一个事务分成两个子过程:

• 过程 1:主控设备 A获得总线使用权后, 获得总线使用权后,将请求的事务类型 将请求的事务类型 将请求的事务类型、地址及其他信息 地址及其他信息 地址及其他信息(如 A的标识等) 发到总线,从设备 B记下这些信息。 记下这些信息。A发完信息后便立即释放总线, 发完信息后便立即释放总线,其他设备便可使用总线 其他设备便可使用总线

• 过程 2:B收到 A发来的信息后, 发来的信息后,按照 A的要求准备数据, 的要求准备数据,准备好后, B便请求使用总线, 便请求使用总线,获使用 权后, B将 A的编号及所需数据送到总线, 的编号及所需数据送到总线,A便可接收

° 请求 - 回答方式 (Request-Reply )

• CPU启动一次读或写事务 - 传送信息:address, data, and command

• 然后等待存储器回答 ° 分离总线事务方式 分离总线事务方式 (Split Bus Transaction )

• CPU启动一次读 /写事务后,释放总线 - 传送信息:address, data (Write ), and command

• 存储器启动一次回答事务,请求使用总线 ,请求使用总线 - 传送信息: data (read) or acknowledge (write) 优点:系统总效率改善 (例如,在存储器存取数据时可以释放总线 ,在存储器存取数据时可以释放总线,以被其他设备使用 ,以被其他设备使用) 缺点: 单独的事务响应时间变长 增加复杂性

例1:同步和异步总线的最大带宽比较

举例:假定同步总线的时钟周期为 :假定同步总线的时钟周期为50ns,每次总线传输花 ,每次总线传输花1个时钟周期,异步总 线每次握手需要40ns,两种总线的数据都是 ,两种总线的数据都是32位宽 ,存储器的取数时间为 ,存储器的取数时间为200ns 。要求求出从该存储器中读出一个字时两种总线的带宽 。要求求出从该存储器中读出一个字时两种总线的带宽。 分析如下: 同步总线的步骤和时间为:

(1)发送地址和读命令到存储器 )发送地址和读命令到存储器:50ns

(2)存储器读数据 )存储器读数据:200ns

(3)传送数据到CPU:50ns 所以总时间为300ns,故最大总线带宽为 ,故最大总线带宽为4B/300ns,即:13.3MB/s。 异步总线的步骤和时间为: 第1步为:40ns; 第2、3、4步为:Max(3x40ns,200ns)=200ns; (第2、3、4步都和存储器访问时间重叠) 第5、6、7步为:3x40ns=120ns。 总时间为360ns,故最大带宽为 ,故最大带宽为4B/360ns=11.1MB/s 由此可知:同步总线仅比异步快大约 同步总线仅比异步快大约20%。要获得这样的速度 。要获得这样的速度 要获得这样的速度,异步总线上 的设备和存储器必须足够快, 的设备和存储器必须足够快,以使每次在40 ns内能完成一个子过程

例2:数据块大小对带宽的影响

假定有一个系统具有下列特性:

(1)系统支持4~16个32位字的块访问。

(2)64位同步总线,时钟频率为200MHz,每个64位数据传输需一个时钟周期,地 址发送到存储器需1个时钟周期。

(3)在每次总线操作(事务)间有两个空闲时钟周期。

(4)存储器访问时间对于开始的4个字是200ns,随后每4个字是20ns。 假定先前读出的数据在总线上传送的同时,随后4个字的存储器读操作也在重 叠进行, 一个总线事务由一个地址传送后跟一个数据块传送组成 , 一个总线事务由一个地址传送后跟一个数据块传送组成 请求出分别用4-字块和16-字块方式读取256个字时的持续带宽和等待时间。并 且求出两种情况下每秒钟内的有效总线事务数。

举例3-数据块大小对带宽的影响

分析 4-字块传送情况: 字块传送情况: 对于4-字块传送方式, 字块传送方式,一次总线事务由一个地址传送后跟一个 一次总线事务由一个地址传送后跟一个4-字块的数据传送组成。 字块的数据传送组成。也 即每个总线事务传送一个4个字的数据块。 个字的数据块。 每个数据块所花时间为: 每个数据块所花时间为:

(1) 发送一个地址到主存花1个时钟周期

(2) 从主存读4个字花:200ns/(5ns/Cycle)=40个时钟周期 (一个周期是109ns/200MHz=1000/200=5ns)

(3) 4个字(128位)的传输需2个时钟周期 (一个64位数据传输需1个时钟周期)

(4) 在这次传送和下次之间有2个空闲时钟周期 所以一次总线事务总共需45个周期,256个字需256/4=64个事务,所以整个传送需 所以整个传送需 45x64=2880个时钟周期,因而总等待时间为 因而总等待时间为 因而总等待时间为:2880周期x 5ns/周期=14400ns。每秒钟的 总线事务数为: 总线事务数为:64 x (1s/14400ns) = 4.44M个。

总线带宽为:(256 x 4B)/14400ns =71.11MB/s。

分析 16-字块传送情况: 字块传送情况: 对于16-字块传送,一次总线事务由一个地址传送后跟一个 一次总线事务由一个地址传送后跟一个16-字块的数据传送组成。 字块的数据传送组成。也即 每个总线事务传送一个16个字的数据块。 个字的数据块。 第一个4-字所花时间为: 字所花时间为:

(1) 发送一个地址到主存花1个时钟周期

(2) 从主存读开始的4字花:200ns/(5ns/Cycle)=40个时钟周期

(3) 传4个字需2个时钟周期,在传输期间存储器开始读取下一个 在传输期间存储器开始读取下一个4字

(4) 在本次和下次之间有2个空闲时钟,此期间下一个4字已读完 所以,16字中其余三个4字只要重复上述最后两步。 字只要重复上述最后两步。因此对于16-字块传送,一次总线事务 共需花费的周期数为: 共需花费的周期数为:1+40+4 x (2 +2) = 57个周期,256个字需256 / 16=16个事务,因此 整个传送需57 x 16 = 912个时钟周期。故总等待时间为 故总等待时间为 故总等待时间为:912周期x 5ns / 周期=4560ns。 几乎仅是前者的1/3。每秒钟的总线事务个数为 。每秒钟的总线事务个数为 每秒钟的总线事务个数为:16 x (1s / 4560ns) = 3.51M个。总线带宽 为:(256 x 4B)x (1s/4560ns) =224.56MB/s,比前者高3.6倍。 由此可见,大数据块传输的优势非常明显 大数据块传输的优势非常明显 大数据块传输的优势非常明显。

增加同步总线带宽的措施

提高时钟频率

° Data bus width(增加数据线宽度)

• 能同时传送更多位 • Example: SPARCstation 20’s memory bus 有 128 bit • Cost: more bus lines ° Block transfers(允许大数据块传送)

• 背对背总线周期,也称为突发(Burst)传输方式

• 只要开始送一次地址,后面连续送数据 ,后面连续送数据 • Cost: (a)增加复杂性 (b)延长响应时间

° Split Bus Transaction(拆分总线事务)

• 一次总线事务时间延长,但整个系统带宽增加 ,但整个系统带宽增加 • Cost: (a) 增加复杂性 (b) 延长响应时间 ° 不采用分时复用方式 不采用分时复用方式 • 地址和数据可以同时送出 • Cost(代价): (a) more bus lines, (b) 增加复杂性

关于I/O总线标准

I/O总线是各类I/O控制器与CPU、内存之间传输数据的一组公用信号 、内存之间传输数据的一组公用信号 线,这些信号线在物理上与主板扩展槽中插入的扩展卡 这些信号线在物理上与主板扩展槽中插入的扩展卡(I/O控制器) 直接连接。 °I/O总线是标准总线,I/O总线标准有:

• ISA / EISA总线:(已逐步被淘汰)

• Multibus总线:(已逐步被淘汰)

• PCI总线:前几年PC机所用的主流标准

• PCI-Express(高速PCI总线):目前PC机所用的主流标准 °I/O总线的带宽 • 总线的数据传输速率(MB/s) = 数据线位数/8×总线工作频率 ×总线工作频率(MHz)×每个总线周期的传输次数

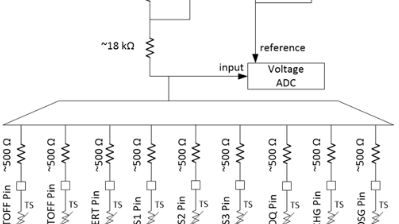

PCI总线标准

(1) 信号线 PCI有50根必须的信号线。按功能可分为以下几组 。按功能可分为以下几组: • 系统信号:包括时钟和复位线。

• 地址和数据信号:包含32根分时复用的地址/数据线、4根分时复用的总线命 令/字节使能线以及对这36根信号线进行奇偶校验的一根校验信号线。

• 接口控制信号:对总线事务进行定时控制,用于在事务的发起者和响应者之 ,用于在事务的发起者和响应者之 间进行协调。

• 裁决信号:它不同于其他信号,不是所有设备共享同一根信号线 ,不是所有设备共享同一根信号线,而是每个 总线主控设备都有一对仲裁线:总线请求和总线允许 :总线请求和总线允许。PCI采用集中式裁决, 所有设备的仲裁线都连接到一个总线裁决器中。

• 错误报告信号:用于报告奇偶校验错以及其他错误。

(2) PCI命令 • 总线活动以发生在总线主控设备和从设备之间的总线事务形式进行。总线主 控设备就是事务的发起者,从设备是事务的响应者,即目标。当总线主控设 。当总线主控设 备获得总线使用权后,在事务的地址周期 ,在事务的地址周期,通过分时复用的总线命令 ,通过分时复用的总线命令/字节使 能信号线C/BE发出总线命令,也即事务类型。

PCI的总线命令(事务类型)有:

• 中断响应:用于对PCI总线上的中断控制器提出的中断请求进行响应。地址线不起 作用,在数据周期从中断控制器读取一个中断向量 ,在数据周期从中断控制器读取一个中断向量,此时C/BE信号线表示读取的中 断向量的长度

• 特殊周期:用于总线主设备向一个或多个目标广播一条消息。

• I/O读和I/O写:I/O读/写命令用于在发起者和一个I/O控制器之间进行数据传送 • 存储器读、存储器行读、存储器多行读 、存储器多行读:用于总线主控设备从存储器中读取数据。 PCI支持突发传送,所以它将占用一个或多个数据周期 ,所以它将占用一个或多个数据周期。这些命令的解释依赖于总 。这些命令的解释依赖于总 线上的存储控制器是否支持PCI的高速缓存协议。如果支持的话 。如果支持的话,那么,与存储器 之间的数据传送以Cache行的方式进行

• 存储器写、存储器写并无效 、存储器写并无效:这两种存储器写命令用于总线主控设备向存储器写数 据,它们将占用一个或多个数据周期 它们将占用一个或多个数据周期。其中存储器写并无效命令用于回写 。其中存储器写并无效命令用于回写Cache行 到存储器,所以它必须保证至少有一个 ,所以它必须保证至少有一个Cache行被写回

• 配置读、配置写:用于一个总线主控设备对连接到PCI总线上的设备中的配置参数 进行读或更新。每个PCI设备都有一个寄存器组(最多可有256个寄存器),这个寄 存器用于系统初始化时对本设备进行配置

• 双地址周期:由一个事务发起者用来表明它将使用64位地址来寻址

存储器读、存储器行读、存储器多行读 、存储器多行读:用于总线主控设备从存储器中读取数 据。PCI支持突发传送,所以它将占用一个或多个数据周期 ,所以它将占用一个或多个数据周期。这些命令的解释 。这些命令的解释 依赖于总线上的存储控制器是否支持PCI的高速缓存协议。如果支持的话 。如果支持的话,那么与存储器之间的数据传送以与存储器之间的数据传送以Cache行的方式进行

(3) PCI数据传送过程 PCI总线上的数据传送由一个地址周期和一个或多个数据周期组成 总线上的数据传送由一个地址周期和一个或多个数据周期组成 上的数据传送由一个地址周期和一个或多个数据周期组成。 所有事件在时钟下降沿(即在时钟周期中间)同步。总线设备在时钟上升沿采样总线信号

(4) PCI总线裁决 采用独立请求方式,有两个独立的裁决线:请求线REQ 和 允许线GNT 总线仲裁器可使用静态的固定优先级法、循环优先级法或先来先服务法等仲裁算法 、循环优先级法或先来先服务法等仲裁算法 采用隐式仲裁方式,在总线进行数据传送时进行总线仲裁,仲裁不会浪费总线周期 ,仲裁不会浪费总线周期

I/O总线,I/O控制器与I/O设备的关系

° I/O设备通常都是物理上相互独立的设备,它们一般通过 ,它们一般通过通信总线与I/O控制器连接 ° I/O控制器通过扩展卡或者南桥芯片与I/O总线连接 ° I/O总线经过北桥芯片与内存、CPU连接

总结

°总线是共享的传输介质和传输控制部件 总线是共享的传输介质和传输控制部件,用于在部件或设备间传输数据 ,用于在部件或设备间传输数据 °总线可能在芯片内 总线可能在芯片内、芯片之间、板卡之间和计算机系统之间连接 、板卡之间和计算机系统之间连接 °I/O总线是I/O控制器与主机之间传输数据的一组公用信号线,它们在物理上与 ,它们在物理上与 主板扩展槽中插入的扩展卡(I/O控制器)直接连接。 °总线可以采用“同步”或“异步”方式进行定时。

• 同步总线用“时钟”信号定时;异步总线用“握手信号”定时

• 可以结合同步和异步方式进行半同步定时通信

• 可以把一个总线事务分离成两个事务,在从设备准备数据时释放总线 ,在从设备准备数据时释放总线(总 线事务分离方式) °总线的裁决:有集中和分布两类裁决方式 :有集中和分布两类裁决方式

• 分布裁决:自举裁决、冲突检测

• 集中裁决:菊花链、独立请求并行判优 、独立请求并行判优

°总线标准(PCI总线) °总线互连结构

• 单总线结构(早期计算机采用 (早期计算机采用)

• 多总线结构(现代计算机采用 (现代计算机采用)

详解显卡全参数

作者本想亲自写介绍关于显卡参数的文章,奈何精力有限。

注:本文转载自:中关村在线 作者:唐磊

手把手教你识别显卡主要性能参数

初识显卡的玩家朋友估计在选购显卡的时候对显卡的各项性能参数有点摸不着头脑,不知道谁对显卡的性能影响最大、哪些参数并非越大越好以及同是等价位的显卡但在某些单项上A卡或者是N卡其中的一家要比对手强悍等等。这些问题想必是每个刚刚接触显卡的朋友所最想了解的信息,可以说不少卖场的销售员也正是利用这些用户对显卡基本性能参数的不了解来欺骗和蒙蔽消费者。今天显卡帝就来为入门级的显卡用户来详细解读显卡的主要性能参数的意义。

关于显卡的性能参数,有许多硬件检测软件可以对显卡的硬件信息进行详细的检测,比如:Everest,GPU-Z,GPU-Shark等。这里我们以玩家最常用的GPU-Z软件来作为本文解析显卡性能参数的示例软件。

GTX590的GPU-Z截图

首先我们对GPU-Z这款软件的界面进行一个大致分区的解读,从上至下共8个分区,其中每个分区的具体含义是:

①.显卡名称部分:

名称/Name:此处显示的是显卡的名称,也就是显卡型号。

②.显示芯片型号部分:

核心代号/GPU:此处显示GPU芯片的代号,如上图所示的:GF110、Antilles等。

修订版本/Revision:此处显示GPU芯片的步进制程编号。

制造工艺/Technology:此处显示GPU芯片的制程工艺,如55nm、40nm等。

核心面积/Die Size: 此处显示GPU芯片的核心尺寸。

③.显卡的硬件信息部分:

BIOS版本/BIOS Version:此处显示显卡BIOS的版本号。

设备ID/Device ID:此处显示设备的ID码。

制造厂商/Subvendor:此处显示该显卡OEM制造厂商的名称。

④.显示芯片参数部分:

光栅操作单元/ROPs:此处显示GPU拥有的ROP光栅操作处理单元的数量。

总线接口/Bus Interface:此处显示显卡和主板北桥芯片之间的总线接口类型以及接口速度。

着色单元/Shaders:此处显示GPU拥有的着色器的数量。

DirectX版本/DirectX Support:此处显示GPU所支持的DirectX版本。

像素填充率/Pixel Fillrate:此处显示GPU的像素填充率。

纹理填充率/Texture Fillrate:此处显示GPU的纹理填充率。

⑤.显存信息部分:

显存类型/Memory Type:此处显示显卡所采用的显存类型,如:GDDR3、GDDR5等。

显存位宽/Bus Width:此处显示GPU与显存之间连接的带宽。

显存容量/Memory Size:此处显示显卡板载的物理显存容量。

显存带宽/Bandwidth:此处显示GPU-Z与显存之间的数据传输速度。

⑥.驱动部分:

驱动程序版本/Driver Version:此处为系统内当前使用的显卡驱动的版本号。

⑦.显卡频率部分:

核心频率/GPU Clock:显示GPU当前的运行频率。

内存/Memory:显示显存当前的运行频率。

Shader/Shader:显示着色单元当前的运行频率。

默认核心频率/Default Clock:显示GPU默认的运行频率。

(默认)内存/Memory:显示显存默认的运行频率。

(默认)Shader/Shader:显示着色单元默认的运行频率。

⑧交火和运算能力部分:

NVIDIA SLI或ATI Crossfire:显示是否开启SLI或者Crossfire多显卡交火。

运算能力:显示是否具备OpenCL、CUDA、PhysX和DirectCompute 5.0运算能力。

下面我们就重点为大将对显卡的性能参数做一个详尽的讲解,最后终结出哪些性能参数最能影响的显卡性能,以及我们消费者在实际购买显卡时应该从哪方面去思考,以及怎么依靠显卡性能参数来对显卡进行大致的判断和比较。我们希望菜鸟读完本文能够对显卡有个大致的“轮廓”,老鸟读完本文能够对显卡的核心性能参数有个更深入的认识。

显卡名称、芯片型号以及硬件信息

显卡名称、芯片型号以及硬件信息

消费者在购买显卡的时候首先应该明确的就是我该购买的显卡的型号(名称)是什么,也就是GPU-Z中的Name所示的参数信息,例如本例中的“GTX590”。

显卡GPU-Z截图中关于显卡名称、芯片型号和硬件信息的部分

而通过显卡芯片型号的解读,我们又可以对显卡核心GPU的信息作进一步的了解。从GPU这一项我们能够得知显卡核心的GPU研发代号。GPU的代号一般来说往往是与显卡型号名称相对应,举例来说:

GF110 对应: NVIDIA GeForce GTX590

GF100 对应: NVIDIA GeForce GTX480

Antilles 对应:Radeon HD 6990

RV870 对应:Radeon HD 5970

当然也有一个GPU代号对应多个显卡型号名称的,而这些往往是JS忽悠小白的地方。例如:

基于GF104核心的显卡同时有NVIDIA GeForce GTX 460 (768MB)、NVIDIA GeForce GTX 460 (1024MB)和NVIDIA GeForce GTX 460SE共三款产品,如果消费者对这些显卡不大熟悉的话,很容量被商家所误导而购买被“换型”的显卡产品。

同型号的三款GTX460的不同区别

从上面的对比图中我们可以很清楚的看到768MB和1024MB版的GTX460主要在显存容量和显存带宽上有很大区别,而GTX460SE的区别主要在于CUDA处理器缩减至了288个。

有同一GPU代号对应多款显卡型号,自然也有同个显卡型号对应多个GPU代号,例如:Radeon HD5670。

HD5670的两种版本

从上图我们可以看到两者的区别主要在于核心GPU、流处理器数量以及核心面积,虽然同为HD5670,但是640SP的HD5670性能已经几乎接近HD5750的程度。

通过上面的总结得知,我们玩家在选购显卡的时候一定要弄明白自己所要购买的显卡型号和显卡GPU核心代号具体是什么,购买的时候最好当场对显卡进行简单的上机测试,用GPU-Z等相关测试软件看下显卡的硬件信息是否有异常情况,这样玩家就可以尽可能的降低上当受骗的几率。

显卡芯片参数解析:悟透ROPs

显卡芯片参数解析:悟透ROPs

这一部分是我们所要重点解读的内容,因为不少初玩显卡的朋友或者老玩家对这些性能参数的都不是特别清晰,下面就让我们来一起进行详尽的解读。

显卡芯片参数部分

首先一个重要的概念就是ROPs(Raster Operations Units),即光栅化处理单元,表示显示GPU拥有的ROP光栅操作处理单元的数量。通常来说:3D图形处理可以分成四个主要步骤,几何处理、设置、纹理和光栅处理,而ROPs就是处理光栅单元 。那么光栅化处理单元的多少对显卡性能有哪些影响了?

ROPs架构图

ROPs(光栅化处理单元)主要负责游戏中的光线和反射运算,兼顾AA、高分辨率、烟雾、火焰等效果。游戏里的AA(抗锯齿)和光影效果越厉害,对ROPs(光栅化处理单元)的性能要求也就越高 ,否则就可能导致游戏帧数急剧下降.比如同样是某个游戏的最高画质效果,8个光栅单元的显卡可能只能跑25帧.而16个光栅单元的显卡则可以稳定在35帧以上。举一个例子:GTX550Ti和HD6790前者是24个ROPs单元,后者是16个ROPs单元,虽然在大部分测试项目中,HD6790都是领先GTX550Ti的,但是在高AA(抗锯齿)负载的情况下,HD6790的弱点即刻暴露出来,16个ROPs单元显得有点力不从心。从FarCry 2中也印证出了这一点:游戏中4xAA设置下HD 6790的落后幅度为4%左右,而开启8xAA后性能落后幅度则扩大至15-17%之多。(关于GTX550Ti和HD6790的ROPs数目,详见于此)

需要注意的是,AMD显卡和NVIDIA显卡在ROPs的设计上是有区别的 ,N卡的ROPs单元和流处理器是“捆绑”的,即置于SIMD之内,所以倘若消减N卡的流处理数量,其ROPs单元也随之消减;而A卡则不一样,其ROPs单元和流处理器单元是没有关联的。

传统管线架构

第二个重要的概念:Shaders。传统管线架构:以往显卡由顶点渲染管线和像素渲染管线组成,生成图像的过程都是先由顶点渲染管线中的Vertex Shader(顶点着色器)生成基础的几何图形骨架(由三角形构成),然后再由像素渲染管线中的Pixel Shader(像素着色器)进行填色,最后才是像素渲染管线中的纹理单元进行贴图。而当新的统一渲染架构提出之后,顶点着色器和像素着色器被合二为一,成为流处理器(Shaders) ,它将同时负责顶点着色和像素着色,避免了负载不均衡的情况发生。最先提出统一渲染架构的是微软的DirectX 10。

步入DX10时代,shader单元数量成为衡量显卡级别的重要参数之一

需要说明的是,N卡和A卡的所采取的核心架构是不一样的,N卡采用的是MIMD架构。多指令流多数据流(MultipleInstructionStreamMultipleDataStream,简称MIMD),它使用多个控制器来异步地控制多个处理器,从而实现空间上的并行性,所以N卡是一个发射器;A卡采用的是SIMD架构设计,即Single Instruction Multiple Data(单指令流多数据流),A卡是将4个简单指令+1个复杂指令打包,再用一个发射器发出。所以A/N两者不能进行流处理器数量的简单对比。

最后我们要解析的是像素填充率(Pixel Fillrate)和纹理填充率(Texture Fillrate)。

像素填充率是指图形处理单元在每秒内所渲染的像素数量 ,单位是GPixel/S(每秒十亿纹理)

像素填充率=核心频率×光栅单元数目/1000

纹理填充速率是指在多边形每个面上填充的颜色的纹理 ,单位是GPixel/S(每秒十亿像素)

纹理填充率=核心频率×纹理单元数目/1000

这两个参数的值在GPU-Z中自然是越大则越能表明显卡所能处理的能力越强悍。并且核心频率是像素填充率(Pixel Fillrate)和纹理填充率(Texture Fillrate)的计算因数,显然显卡核心频率越高,这两个值越大。而其中的光栅单元数目即ROPs的值,ROPs的值越大,像素填充率也就越大。

显存参数别忘了“位宽兄弟”

显存的作用,说通俗点,其实和我们机器内部所使用的内存的作用是几乎相同的。卖场里的销售人员也经常对显存这个“卖点”来进行相关“炒作”,当然不少“小白”也因此上当受骗。下面显卡帝就来为初级玩家进行相关解析。

GPU-Z截图关于显存的部分

Memory Type(显存类型),现如今,最新的主流高端级显卡都采用的是GDDR5的显存颗粒,之前主流的GDDR3显存颗粒也正式退役至二线,而GDDR4显存颗粒仅仅是个过渡型产品,市售的显卡所见不多。GDDR5相对于GDDR3的核心优势在于显存带宽大幅度提升 。

显存带宽(Bandwidth)=(显存位宽 ×显存工作频率)/ 8

从上面的计算公司我们可以清楚的看到,由于GDDR5显存颗粒具备两条数据总线,所以虽然采用的是和GDDR3同样的8位预取机制,但显存的工作频率可以到达GDDR3的两倍。最为典型的一个例子就是:采用GDDR5显存的GT240显卡要比采用GDDR3显存的GT240显卡性能领先16%左右,所以凭借强大的带宽优势,GDDR5在同位宽的情况下可以全面超越GDDR3。

Bus Width(位宽)往往是玩家最容易忽视的一个概念。显存位宽是显存在一个时钟周期内所能传送数据的位数,位数越大则瞬间所能传输的数据量越大 。可以说显存位宽对显卡性能的影响相比显存容量而言要大不少。

显卡对阵图

显卡显存位宽的权重到底有多大了,我们从上面这张显卡对阵图中来一起找找答案。从大部分媒体的测试结果来分析,我们给上述显卡在性能上进行一个简单的排序。

HD6850 > HD6790 > GTX550Ti > HD5770

我们重点关注下HD6790和GTX550Ti这两款显卡,虽然说GTX550Ti在核心频率和ROPs数量上均高于HD6790,但是在大部分的测试项目中为何又败下阵来了?首先HD6790采用的HD6850的缩减核心架构这一点自然不用说,其二就在显存位宽上,GTX550Ti仅为192Bit位的显存位宽,所以显存带宽的处理能力仅为98.4GB/S,而HD6790则采用的是256Bit的显存位宽,显存带宽处理能力达到了134.4GB/S,相比GTX550Ti提升36.58%。而为什么GTX550Ti相比HD5770来说,又能够将HD5770全面压制了,其实道理也是一样的。从显存带宽(Bandwidth)=(显存位宽 ×显存工作频率)/ 8 这个公式我们也可以看到当都采用GDDR5显存颗粒的时候,显存位宽就成为了影响性能的关键瓶颈 。

最后我们需要提醒玩家注意的是显存容量(Memory Size)这个最经典的“骗局”,就是利用A卡的Hyper Memory(HM)或N卡的Turbo Cache(TC)的动态共享系统内存技术来谎称显卡的显存容量,想必这样的招数在进过前些年的“洗礼”之后,现在的不少消费者也逐渐对这样的雕虫小技都能够很快的精准识别。

显卡频率:核心频率>显存频率

显卡的频率,我们主要关注的是核心频率和显存频率。两者相比较而言,核心频率对显卡性能的影响权重较大。所以我们玩家在超频的时候先提升的核心频率,再才是显存频率。为什么说核心频率的重要性更大一些了?打个比方,核心频率就相当于个人自身能力,而显存频率好比外在条件,而一个人的成功往往取决于个人能力而外在条件仅在一定程度上对其有影响,简而言之:一个是内因而另一个是外因 。

GPU-Z中关于显卡频率部分的截图

需要说明的是由于核心架构的设计不同,N卡的GPU核心频率和Shader频率呈现2倍的关系,而A卡的GPU核心频率和Shader频率是一致的。

显存频率是指默认情况下,该显存在显卡上工作时的频率,以MHz(兆赫兹)为单位。

GDDR5显存颗粒

关于GDDR5显存频率,由于以往GDDR1/2/3/4和DDR1/2/3的数据总线都是采用的DDR技术(通过差分时钟在上升沿和下降沿各传输一次数据),官方标称的频率X2就是数据传输率,也就是通常我们所说的等效频率。而GDDR5则不同,它有两条数据总线,相当于Rambus的QDR技术,所以官方标称频率X4才是数据传输率 。比如GTX590官方显存频率是854MHz,而大家习惯称之为3416MHz。

现在我们已经知道了显卡频率的对显卡性能的影响,有个问题我们需要提出来讨论一下:显卡频率是不是越高越好?

从旗舰显卡的频率设定来看,它们的核心频率设定都不是特别高,而且前段时间也爆出:AMD对HD6990因超频而致使显卡损坏的显卡用户不予质保,同时也有国外媒体在测试GTX590显卡的时候所出现的“烧毁”显卡的现象。由此可见,高频设定的高端显卡由于GPU核心温度的极高无比而致使显卡烧毁这样的一种玩卡方式确实有些不大妥当。毕竟玩家还是自己的显卡能够稳定运行。当然,在中端显卡上我们也可以看到风冷情况下高频设定的显卡,例如新近推出的GTX550Ti,1G核心频率设定的显卡产品也有一些。高频显卡的意义何在,从另一个角度去分析:不妨作为一种检测显卡品质的方法,因为能够在高频下运行的显卡需要很好的做工和强劲的显卡散热器做支持。其实我们玩家在大部分情况下应用的也就是显卡的默认频率设定,所以高频设定的显卡,我们也很担心其寿命的长短。故而我们并不推荐玩家刻意的追求极致高频,除非你是一个狂热的超频玩家。

驱动、交火和其他运算能力

显卡的性能的表现在有些程度上与显卡驱动存在着一定的关系,因为GPU厂商会对显卡做针对性的优化。所以我们推荐玩家选择最新版的WHQL版驱动来体验你的显卡。

驱动、交火和运算能力

SLI和Crossfire技术提供了多卡互联的技术解决方案。关于什么样的显卡组建多卡互联系统会显得更具性价比了?个人建议采用中断显卡组建系统会显的更划算一些,当然资金充裕的话,采用中高端显卡来组建多卡互联系统也可以,如果采用低端的显卡来组建交火的话,这样就不大太划算,因为可能低端显卡组建的平台性能优势才仅仅相当于中端卡的能力,而价格却已经超过了单块中端显卡的价钱。

SLI速力技术平台

Crossfire交叉火力技术平台

最后我们来看看Computing计算能力这一项,OpenCL(全称Open Computing Language,开放运算语言)、CUDA(通用并行计算架构)、PhysX(物理加速)和DirectCompute 5.0(是一种用于GPU通用计算的应用程序接口)。

AMD HD6990的相关截图

对比A卡,N卡在Computing这项的表现上显得更加出色,N卡全部支持四项运算能力,而A卡仅支持一项DirectCompute 5.0。倘若玩家对借助CUDA技术实现高清转码或者玩的游戏需要PhysX物理加速技术的支持,那么玩家可以考虑购买N卡,因为这些正是N卡所强势的地方。

总结:“显卡性能参数排排坐”

进过了前面详细的介绍与分析,我们对显卡的主要性能参数有了一个相对全面的认识和了解。玩家在购买显卡的时候,可能对这么多性能参数“有点晕”,所以我们有必要对这些显卡性能参数的权重进行一个高低顺序的排序。下面是笔者所总结的一个相对简洁的显卡性能排序:

①显卡核心和制程

显卡核心是关键,核心不行其他再好都是浮云,核心先进那么显卡的性能自然会提升一个很大的档次;制程越先进,显卡的发热量和功耗越低。

②流处理器和ROPs

流处理器数量上的增加或缩减对显卡的性能影响可谓是立竿见影,所以GPU厂商也常常利用这一方法来对显卡产品进行市场细分。ROPs数量的多数影响在游戏画面中的AA(抗锯齿)和光影特效等方面。

③核心频率和显存频率

核心频率影响的是像素填充速率和纹理填充率,而显存频率影响的是显存带宽,两者同时都作为影响因子,所以参数值越大,自然显卡性能越强悍。不过过高的频率设定对显卡自身有一定影响,合理的频率设定是我们所要选择的显卡。

④像素填充速率和纹理填充率

像素填充率=核心频率×光栅单元数目/1000

纹理填充率=核心频率×纹理单元数目/1000

⑤显存位宽和显存带宽

显存带宽=工作频率×显存位宽/8(显存带宽 =显存位宽×显存频率/8/1024)

显存位宽越大,那么瞬间所能传输的数据量越大。显存带宽的作用好比桥梁一样,为显示核心和显存提供了一条交换数据的通道。

⑥显存大小和其他参数

显存太小的话会导致在游戏过程中有帧数不稳定的显示。

以上排序作为玩家在购买显卡时分析性价比的几个方面,当然顺序并非完全固定,具体还得需要考虑到玩家自身对显卡的详细要求。但是有一点是肯定的,知道这些决定显卡性能的参数,我们玩家在购买显卡或与人谈论显卡的时候会显得更加专业,让JS从此惧怕小白,这就是为您写下此文的最终目的。

相关问答

如何理解CPU的数据总线宽度?CPU重要参数介绍:1.前端总线:英文名称叫FrontSideBus(FSB)。前端总线是CPU跟系统沟通的通道,处理器必须通过它才能获得外部数据,也需要通过它来将...CPU...

bbv表示什么电线?bbw是总线带宽的意思,英文全称是:busbandwidth。对于电子电路中的带宽,决定因素在于电路设计。它主要是由高频放大部分元件的特性决定,而高频电路的设计是...

求这个交通标志的英文连续弯路_作业帮[回答]急救站Firstaidstation禁令标志Prohibitionsign客轮码头Passengerquay指示标志Mandatorysign餐饮Restaurant指路标志Gu...

brt的标准大小?答:有12米和18米两种。快速公交系统(BusRapidTransit)是一种介于快速轨道交通与常规公交之间的新型公共客运系统,其投资及运营成本比轨道交通低,而运营效...

服务器主板上的BMC是什么意思?BMC:基板管理控制器BaseboardManagementControllerBMC(BaseboardManagementController,基板管理控制器)支持行业标准的IPMI...

简述cpu的接口类型和主要性能指标?CPU的接口类型:NTERCPU针脚数常见的是:478和775AMD的CPU常见的有:939940603604CPU主要的性能指标有:(1)主频即CPU的时钟频率(CPUClock...

BBW什么意思?bbw是总线带宽的意思,英文全称是:busbandwidth。对于电子电路中的带宽,决定因素在于电路设计。它主要是由高频放大部分元件的特性决定,而高频电路的设计是...

【英语交通标志翻译翻译多的给分``全部交通标志都要翻译,】作...[回答]警告标志Warningsigns禁令标志Bansign指示标志indication指路标志Thesign辅助标志Auxiliarysign╮(╯▽╰)╭警告标志Warningsigns禁令...

微型计算机总线一般有哪几个总线组成 - 小眼睛大Lorry 的回答...(1)、总线的定义总线是计算机各设备间进行信息传输的通道。它由数据总线、地址总线、控制总线组成。数据总线是外部设备和总线主控设备之间进行数...

显卡的重大参数主要看什么?-ZOL问答型号RopsTMUCUDABuswidth具体显卡GK110482402880384bitGTX780Ti/GTXTitanBlackGK1104822426883...