源同步接口设计1master篇

大家好,我是七点班车。记得之前跟朋友说自己撸的SPI NAND FLASH主控能够跑133MHz,朋友很诧异说:“SPI怎么可能跑这么高?”我也很愤怒——事实就摆在这,怎么可能跑不了?到底是哪里来的勇气,让他“口出狂言”,怀疑我的设计?。。。

接下来就用两篇文章来捋一捋鄙人对“源同步接口设计”的一些思考与见解。今天先上Master篇。

Master接口的瓶颈源同步接口在设计中十分常见,例如SPI接口,async NAND FLASH接口。这类接口的时钟由master生成,并经过IO发送到slave中。对master的第一级寄存器来说,有着一段非常长的launch path(如图1.1所示):时钟源S点到IO clk_o -> clk_o到reg1/clk ->reg1/clk到IO data_i -> data_i到reg0/D,如红色曲线,而capture path(时钟源S点到reg0/clk)相对比较短,如蓝色曲线。

图1.1

对于launch比较长,capture path比较短的路径,hold一般都不会有什么问题。但是setup就不一样了,launch path太长,则有可能导致下面公式不满足,从而带来setup违例。因此,接下来,我们就基于setup来讨论下这种源同步接口的设计问题。

为了能够更直观地分析,我们先来看看图1.2的波形图,其中最下面的黑色双向箭头为reg0的setuphold窗口(因为没搞懂怎么用timegen怎么画这窗口,所以只能凑合凑合了)。那么为了保证reg0能够正确地采样,D0必须在setuphold窗口之前保持稳定。用数学式来表示就是,reg0要能正确采样,必须要满足公式(1)。

tlaunch < T + tcapture - tsetup,其中tlaunch= ts2clk_o+tclk_o2clk + tclk2data_i + tdata_i2D,tcapture = ts2clk ——公式(1)

图1.2

我们将图1.1中的数值代入到公式中,可得:2+3+5+4<T+1- tsetup。由于tsetup比较小,这里暂且忽略不计。故可退出T>15ns,即接口的最大频率Freq_max=76.9MHz。天。。。。。。瓶颈在这!

提高频率的技巧(非设计层面)如果要提高频率,要怎么办?我想答案已经很明显了,要么削短tlaunch,要么做长tcapture。

1. 在PCB layout中,将layout线延时tclk_o2clk和tclk2data_i做短。(由于兼容性等客观问题,这个往往不受我们控制)

2. 选用延时比较小的PAD(但是,在穷逼的公司,PAD不是说有就有的——骄傲的工程师可以天马行空,但是有时候又不得不接受骨干的现实)。

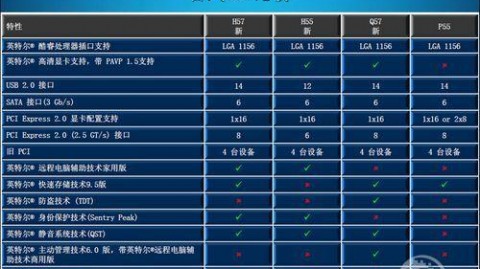

3. 在SDC中,将ts2clk_o 和tdata_i2D做短,具体做法是,将clk_o的output delay和data_i的input delay设大,即留给chip内部的delay变小。在STA中,需要格外关注,并把它做短,表1.1是鄙人在项目中统计的tdata_i2D真实值。

表1.1

4. 在PR或者STA fix timing的过程中,将ts2clk做长。但是这样子的做法,有可能会给后面的寄存器带来新的setup问题,如图1.3的reg2。所以一般不会这么干。

图1.3

然而,在某种程度上,IC设计上的问题就跟戴绿帽一样,发现得越晚,就越难!所以如果把问题推到STA再去解决的话,可能就是“好吃不过饺子。。。”的梗了。因此,能在设计上动刀,就动吧。

提高频率的技巧(设计增加采样点)

咱再来回顾下公式(1),tsetup 是寄存器的特有属性,改不了;除了上面提到的tlaunch和 tcapture,公式中还有一个“T”,我们能否在设计上将它“搞大”?

对于同源接口来说,slave就像个机器,它会严格按照协议规定来进行工作。就拿图1.4的SPI NAND FLASH(截图来自复旦微的手册)来说,在接收到命令后,经过一个dummy byte,也就是在第15个时钟下降沿,slave就必须把ID送出来。

图1.4

而Master占据了所有的主动权,毕竟它才是生成时钟的主。如果数据在第16个时钟上升沿到达不了,而是在第17个上升沿才到达,那Master也是可以在第17个上升沿才对数据进行采样的。因此,我们在设计Master的时候,可以适当增加一些采样点,每个采样点的间隔是半个周期,如图1.5粉色标号1/2/3/4所示。当D0在采样点1上出现违例时,可以把使用采样点2的数据,而对于采样点2来说,就增加了T/2。依次类推。。

图1.5

图1.6亮出了部分参考代码,自己慢慢体会吧。

图1.6

STA需要关注的bus对齐问题谈到接口,就多少会涉及bus;涉及bus,就得关注对齐问题。如图1.7,假设reg0/D和reg3/D是数据bus,且这两个信号在电路上会出现重聚。从图中可以看出,无论是在采样点2,还是在采样点3中,就只能采到reg0/D和reg3/D中的一个。显然,两者重聚后,注定是个悲剧。因此,我们在STA中需要格外关注bus skew,不能让它超过半个周期。

图1.7

以上就是今天要分享的内容。谢谢大家!请关注我的公众号:"IC小迷弟"@

Nand Flash主要厂商及其产品

根据2020年二季度Nand Flash市场排名,三星占据31%,处于领先地位,紧跟其后的是铠侠,占比达17%。排名第三、第四、第五、分别是西数、美光、SK海力士。以下是DRAMeXchange统计数据:

电子发烧友对目前市场主要的Nand Flash厂商及其产品进行梳理,以下是具体内容:

三星

1、三星SSD 980 PRO

三星电子推出首款消费类PCIe 4.0 NVMe SSD:三星SSD 980 PRO, 980 PRO采用三星1XX层 TLC NAND闪存,以及容量分别为512MB和1GB的DRAM缓存,通过内部设计,可充分发挥PCIe Gen4的潜力。数据显示,三星SSD 980 PRO顺序读取速度最高可达7000MB/s,顺序写入速度最高可达5000MB/s。

2、870 QVO SATA SSD

三星推出了其第二代QLC闪存驱动器870 QVO SATA SSD, 870 QVO分别提供同类最佳的顺序读取和写入速度,分别高达560 MB/s和530 MB/s,借助该驱动器的Intelligent TurboWrite技术,它可以使用大型可变SLC缓冲器保持最高性能

3、eUFS 3.1

三星电子宣布已经开始批量生产用于智能手机的512GB eUFS 3.1,其写入速度为512GB eUFS 3.0的三倍,打破了智能手机存储中1GB/s的阈值。

三星eUFS 3.1连续写入速度超过1,200MB/s,是基于SATA SSD (540MB/s)的两倍以上,是UHS-I microSD卡(90MB/s)的十倍以上。

KIOXIA

1、第六代企业SAS SSD

随着其第六代企业SAS SSD系列的推出, 专为现代IT基础设施设计的24G SAS将其上一代的数据吞吐率提高了一倍,同时搭载了新功能和增强功能,以达到新的应用性能水平。

PM6系列采用铠侠的96层BiCS FLASH 3D TLC闪存,可提供业界领先的高达4,300MB/s(4,101MiB/s)的SAS SSD顺序读取性能,比上一代提高了2倍以上。铠侠的新驱动器容量高达30.72TB,使其成为业界容量最高的2.5英寸SAS SSD。

2、BiCS FLASH

铠侠开发具有112层垂直堆叠结构的第五代BiCS FLASH™三维(3D)闪存。新产品具有512 Gb(64千兆字节)容量并采用TLC技术。

铠侠创新的112层堆叠工艺技术与先进的电路和制造工艺技术相结合,与96层堆叠工艺相比,将存储单元阵列密度提高约20%。因此,每片硅晶圆可以制造的存储容量更高,从而也降低了每位的成本(Bit-cost)。此外,它将接口速度提高50%,并提供更高的写性能和更短的读取延迟。

西部数据

1、SN550 NVMe SSD

Western Digital设计的控件和固件搭配最新的 3D NAND,可始终如一地提供优化的性能。

2、iNAND MC EU521

西部数据宣布率先基于UFS 3.1规范协议推出iNAND MC EU521嵌入式闪存产品,新增多项功能,并进一步提高速度、容量、降低功耗,再加上11.5x13x1.0mm小型封装尺寸。西部数据表示,iNAND MC EU521将在3月份上市,采用主流的96层3D NAND,并充分利用UFS 3.1高带宽以及SLC NAND缓存,可提供最高800MB/s的顺序写入速度。

美光

美光的下一代 M500 固态硬盘采用 Micron 20 nm MLC NAND 闪存、SATA 6 Gb/s 接口,具有行业标准 512 字节分区支持功能、热插拔功能以及功耗极低的器件休眠模式,并满足 ATA-8 ACS2 指令集规范要求。

SK海力士

Intel 突然宣布以 90 亿美元(约 601 亿)的价格将旗下的 NAND 闪存业务出售给了 SK 海力士 ,后者有可能成长为新的全球第二大闪存公司,SK海力士推出Gold P31系列SSD新品,是全球首个基于128层NAND闪存的消费者SSD。Gold P31采用的是128层TLC,PCIe NVMe Gen3接口,读取速度最高达3500MB/s,写入速度最高达3200MB/s,以满足长时间游戏的游戏玩家以及对性能和稳定性有较高要求的专业创作者和设计师。

英特尔

Intel基于144层3D QLC闪存Arbordale Plus,容量将比Intel目前的96层产品提升50%。

长江存储

128层QLC 3D NAND闪存芯片X2-6070研发成功,并已在多家控制器厂商SSD等终端存储产品上通过验证。

长江存储表示,X2-6070是业内首款128层QLC规格的3D NAND闪存,拥有业内已知型号产品中最高单位面积存储密度,最高I/O传输速度和最高单颗NAND闪存芯片容量。

每颗X2-6070 QLC闪存芯片共提供1.33Tb的存储容量。而在I/O读写性能方面,X2-6070及X2-9060均可在1.2V Vccq电压下实现1.6Gbps(Gigabits/s千兆位/秒)的数据传输速率。

旺宏

Macronix在2020年下半年生产48层3D NAND存储器。公司计划在2021年和2022年分别推出96层3D NAND和192层3D NAND。目前,该公司用于制造NAND的最先进技术是自2019年2月开始使用的19纳米平面技术,这款NAND Flash的第一个客户将是任天堂。

华邦

1、QspiNAND Flash

华邦提供了一系列相容于SPI NOR接口的QspiNAND产品,华邦的QspiNAND系列产品内建了ECC的功能,而且也能提供了连续好”块”的QspiNAND,这些都能让使用者并不需要额外的控制器。

2、OctalNAND Flash

全球首款采用x8 Octal接口的NAND Flash—华邦OctalNAND Flash产品可望提供车用电子与工业制造商高容量的储存内存产品,华邦电子首款采用全新接口的NAND产品,1Gb W35N01JW,连续读取速度最高可达每秒240MB, W35N-JW OctalNAND Flash采用华邦通过验证的46nm SLC NAND制程,提供卓越的数据完整性,且数据保存期更可达10年以上。此产品写入/抹除次数(Program/Erase Cycle)可达10万次以上,可符合关键任务型车用与工业应用所需的高耐用性与高可靠性。

兆易创新

GD5F4GM5系列采用串行SPI接口,引脚少、封装尺寸小,相比于上一代NAND产品,大大提升了读写速度,最高时钟频率达到120MHz,数据吞吐量可达480Mbit/s,支持1.8V/3.3V供电电压,能够满足客户对不同供电电压的需求;同时提供WSON8、TFBGA24等多种封装选择。

北京紫光存储

北京紫光存储Raw NAND颗粒是符合业界标准的闪存产品,适用于各类固态存储解决方案。Raw NAND颗粒需要搭配闪存控制器使用。全系采用业界领先的3D TLC闪存芯片。支持ONFI 4.0,最高读写支持667MT/s。采用业界领先的3D TLC闪存芯片,相比2D闪存芯片单位面积下容量大幅提升。

北京君正

公司Flash产品线包括了目前全球主流的NOR FLASH存储芯片和NAND FLASH存储芯片,其中NAND FLASH存储芯片主攻1G-4G大容量规格。

ISSI 系一家原纳斯达克上市公司,于 2015年末被北京矽成以7.8亿美元私有化收购,之后北京君完成对北京矽成100%股权收购。ISSI Introduces SLC NAND高性能4Gb SLC NAND主要用于嵌入式市场,能够满足工业、医疗,主干通讯和车规等级产品的要求,具备在极端环境下稳定工作、节能降耗等特点。

东芯

东芯串行NAND Flash产品为单颗粒芯片设计的串行通信方案,引脚少和封装尺寸小,且在同一颗粒上集成了存储阵列和控制器,带有内部ECC模块。使其在满足数据传输效率的同时,既节约了空间,提升了稳定性,也让其在成本上也极具竞争力,且提升了性价比。产品分为3.3V/1.8V两种电压,不仅能满足常规对功耗不敏感的有源器件,也使其在目前日益普及的移动互联网及物联网设备中,有足够的发挥空间。产品拥有多种封装,可更灵活的满足很多应用场景,比如常规的光猫,路由器,网络摄像监控,物联网及智能音箱等。

相关问答

怎么样在PPT上,插入一个与计算机时间同步的钟表?-ZOL问答3.在面板中,单击右下角的“其它控件”,从下拉列表中选择“ShockWaveFlashObject”选项。然后使用鼠标拖动一个长方形区域出来以便插入Flash时钟。4.右键单...

flash 钟表怎么制作基本的思路我是会的.就是分针、秒针、时针...[最佳回答]root.createEmptyMovieClip("s_mc",100);s_mc._x=150;s_mc._y=150;s_mc.lineStyle(2,0x...

嵌入式开发,请问学习嵌入式的时候,是否需要先学习别 - Deha...成为一名嵌入式Linux开发工程师需要学习哪些知识?随着嵌入式行业的迅猛发展,嵌入式Linux凭借其系统发展的成熟度、市场应用的高份额也受到更多工程...

哪有 flash 元件素材下载?站长素材FLASH动画栏目,提供透明flash素材、flash时钟、flash模板、flash相册、flash菜单、flash片头、flash广告、flash按钮等flash动画素材下载。站长素材F...

DRAM和RAM的区别是什么?DRAM这东西到底有什么用呢? - 136****...ROM和RAM指的都是半导体存储器,ROM是ReadOnlyMemory的缩写,RAM是RandomAccessMemory的缩写。ROM在系统停止供电的时候仍然可以保持数据,而RAM通常都...

flash 读取会导致数据丢失吗?1、用户代码对Flash的误操作不当引起程序丢失或被错误改写例如,在有对Flash写入或擦除操作的代码中,如果用户误调用了写入或擦除函数或者由于程序跑飞而恰好...

eeprom与 FLASH 的区别?flash是用来存储代码的,在运行过程中不能改;EEPROM是用来保存用户数据,运行过程中可以改变,比如一个时钟的闹铃时间初始化设定为12:00,后来在运行中改为6:...

PPT演示的时候,怎么做到时间控制-ZOL问答1、在PPT母板的角落里插入一个flash时钟,放映时每页上都会有实时的时间显示。具体过程如下图,需要先百度下载一个显示时间的flash时钟文件。2、在PPT的母板视...

怎样在自己 的博客里加上一个可爱的钟 - NBKK 的回答 - 懂得时钟样式具体步骤:进入“控制面板”——首页内容维护——自定义空白面板——新增——勾选“显示源代码”(这个是关键)——在编辑区粘贴以上代码(字...

如何添加钟表 - 178****3035 的回答 - 懂得时钟源代码:代码说明:width=180height=180是Flash的宽度和高度,可以自定义设置。具体的操作步骤是:1,先把下面你选中的时钟代码贴入“地址”栏内。(...